# Experimental Validation of Crosstalk Simulations for On-Chip Interconnects Using S-Parameters

Mauro J. Kobrinsky, Sourav Chakravarty, Dan Jiao, Michael C. Harmes, Scott List, and Mohiuddin Mazumder

Abstract—Since the design of advanced microprocessors is based on simulation tools, accurate assessments of the amount of crosstalk noise are of paramount importance to avoid logic failures and less-than-optimal designs. With increasing clock frequencies, inductive effects become more important, and the validity of assumptions commonly used in simulation tools and approaches is unclear. We compared accurate experimental S-parameters with results derived from both magneto-quasi-static and full-wave simulation tools for simple crosstalk structures with various capacitive and inductive couplings, in the presence of parallel and orthogonal conductors. Our validation approach made possible the identification of the strengths and weaknesses of both tools as a function of frequency, which provides useful guidance to designers who have to balance the tradeoffs between accuracy and computation expenses for a large variety of cases.

Index Terms—Interconnects, on-chip, S-parameters, signal integrity, validation.

# I. INTRODUCTION

PRESENT advanced microprocessor designs rely heavily on simulation results, since time and resource constraints make impossible the experimental assessment of all cases of interest. Inaccuracies in the estimated crosstalk noise could result in logic failures and less-than-optimal designs. Furthermore, the uncertainties associated with simulation tools that have not been validated typically translate into conservative nonoptimal designs. Unfortunately, obtaining the high-quality experimental data at high frequencies (tens of gigahertz) that is needed to validate simulation tools is challenging because of parasitics that can significantly distort the experimental results.

A complete experimental validation using structures implemented in a full flow Si testchip with drivers and receivers can potentially provide realistic results to investigate signal integrity, but it would require significant layout time and manufacturing expenses and is usually not a practical option. In addition, active Si measurements of crosstalk noise are typically indirect and benefit greatly when combined with passive measurements. On the other hand, the relatively low cost of passive-structure testchips (i.e., without active Si devices) provides the opportunity for fabricating and testing hundreds

Manuscript received March 4, 2004.

- M. J. Kobrinsky and M. C. Harmes are with the Components Research Department, Intel Corporation, Hillsboro, OR 97124 USA (e-mail: mauro.j. Kobrinsky@intel.com).

- S. List is with the Interuniversity MicroElectronics Center (IMEC), B-3001 Leuven, Belgium (e-mail: scott.list @ intel.com).

- S. Chakravarty is with the Technology Computer-Aided Design (TCAD) Group, Intel Corporation, Hillsboro, OR 97124 USA.

- D. Jiao and M. Mazumder are with the TCAD Group, Intel Corporation, Santa Clara. CA 95054 USA.

Digital Object Identifier 10.1109/TADVP.2004.841672

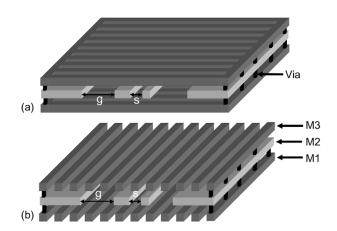

Fig. 1. Schematic of the crosstalk structures, indicating the definition of the parameters s and g. Line widths are 1 and 2  $\mu$ m. (a) Structures with orthogonal wires in M1 and M3 (OR1–OR4). (b) Structures with parallel wires in M1 and M3 (P1).

of test structures, which facilitates the identification of the underlying physical mechanisms that govern signal integrity.

In this paper, we investigate the behavior of simple passive crosstalk structures in which we varied key physical dimensions (e.g., spacings and lengths), as well as the orientation of the conductors in the layers above and below the signal lines, to obtain different levels of inductive and capacitive couplings. The test structures were experimentally characterized by measuring the S-parameters and removing the parasitics using a de-embedding approach that we developed. In addition, we used a quasimagneto-static and a full-wave simulation tool to predict the electrical behavior of the test structures, which we then compared to the experimental results to identify their strengths and weaknesses.

# II. EXPERIMENTAL

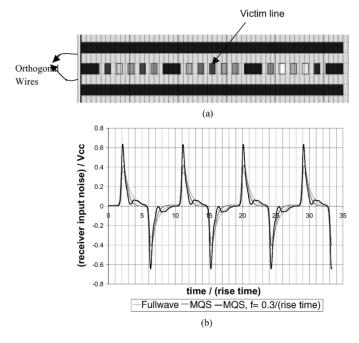

We considered passive test structures fabricated using three levels of metal, to which we will refer as M1, M2, and M3 [Fig. 1(a) and (b)]. The structures basically consisted of two parallel signal lines in M2, wide solid returns in M2, and additional returns of two different types in M1 and M3. One of the signal lines in M2 was 1- $\mu$ m wide while the other was 2- $\mu$ m wide. Structures OR (OR1, OR2, OR3, OR4) have 50% dense conductors in M1 and M3 (i.e., the Cu conductors occupied 50% of the total area), formed by 1- $\mu$ m-wide lines running perpendicular to the M2 signal lines as shown in Fig. 1(a). Structures P1 have 50% dense returns in M1 and M3 composed of 1- $\mu$ m-wide lines running parallel to the signal lines as shown in Fig. 1(b). By varying the distance between the signal lines (s2) and the distance between signal lines and returns in M2

|                      | OR1        | OR2        | OR3        | OR4        | P1       |

|----------------------|------------|------------|------------|------------|----------|

| s2                   | 0.19 μm    | 0.18 μm    | 1.98 µm    | 1.95 µm    | 2.0 µm   |

| g2                   | 1.0 µm     | 10.2 μm    | 0.98 μm    | 10.3 μm    | 10.7 μm  |

| M1 and M3 conductors | Orthogonal | Orthogonal | Orthogonal | Orthogonal | Parallel |

TABLE I

CROSSTALK STRUCTURES CONSIDERED IN THIS PAPER

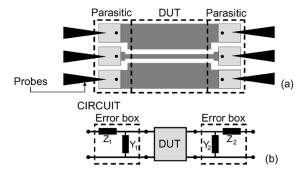

Fig. 2. (a) Schematics of a test structures. (b) Circuit model, showing the parasitics sources and the DUT.

(g2), different levels of capacitive and inductive couplings were obtained. Table I summarizes the dimensions of the crosstalk structures, which were measured using high-resolution scanning electron microscope (SEM) cross sections and optical microscopy. A single value of line length (2 mm) is considered for the OR structures, and two different line lengths are used for P1 (2 and 8 mm). The dc resistivity of the Cu lines was obtained by measuring the total resistance of lines of different lengths, and was found to be  $1.97~\mu\Omega$ -cm. The effective dielectric constant of the combined Si and Si nitride layers was measured at 1 MHz. For both M2 signal lines, one of the ends was left open, while the other was connected to a bondpad, resulting in two-port structures [see Fig. 2(a)]. Since the bondpads were both on the same side of the lines, the measurements corresponded to the so-called near end crosstalk noise.

The electrical behavior of the structures was experimentally characterized by measuring their S-parameters in the frequency range 45 MHz–40 GHz, using an HP8510 system. The dimensions of the bondpads were  $50 \times 35~\mu m^2$ , which were probed with  $50~\mu m$ -pitch ground-signal-ground microwave probes. It is relevant to mention that the cables used in the measurements and geometry of the test structures only enables transverse electromagnetic (TEM) waves in the frequency band of interest. However, in practice, it may be possible to have non-TEM waves excited. Such scenarios are not considered in this paper.

The S-parameters,  $S_{ij}$ , of two port structures form a matrix of rank 2:  $S_{11}$  is the reflection at port 1, while  $S_{12}$  represents the crosstalk between ports 1 and 2. Two important advantages of S-parameters are that: 1) they can be accurately measured, and 2) they allow accurate de-embedding of parasitics (will be discussed later). In addition, they also provide a direct measure of the amount of crosstalk at *each* frequency  $(S_{12})$ , which is of great importance since, as we will show later, the amount of crosstalk strongly depends on frequency in a

nonmonotonic manner, and can increase or decrease with increasing frequency, which prevents the direct extrapolation of crosstalk from single-frequency information. Finally, it is important to mention that, given the S-parameters and the reference impedance (50  $\Omega$  in this work), the time-domain response can be calculated for any excitation and loading condition. On the contrary, a given time-domain result (i.e., voltage–time) is only valid for the particular rise time, pulse shape, and termination conditions of the experiment.

To measure the response of the signal lines, we need cables, probes, bondpads, access lines, and vias [Fig. 2(a)]. Unfortunately, these additional elements also contribute to the measured  $S_{ij}$  in a complicated frequency-dependent manner. The removal of these undesirable signals, referred to as parasitics, is a difficult task that has hindered many previous validation attempts. The parasitics introduced by the cables and the probes were removed following the well-known short-open-load-thru (SOLT) technique [1] using a calibration substrate (i.e., off die). To remove the remaining parasitics generated by the bondpads, vias, and access lines, we developed a de-embedding technique that builds upon the YZ-matrix technique, and that allowed us to accurately remove the parasitics. We modeled the parasitics with general frequency-dependent Z and Y elements [Fig. 2(b)], which are unknown.

Mathematically, it is convenient to use [ABCD] matrices, which allow cascading of elements in series [1]. If the Y and Z parameters are given, the ABCD matrix of the device under test (DUT) can be obtained using

$$\begin{pmatrix} a & b \\ c & d \end{pmatrix}_{\text{DUT}} = \begin{pmatrix} 1 + Y_1 Z_1 & Z_1 \\ Y_1 & 1 \end{pmatrix}^{-1} \cdot \begin{pmatrix} a & b \\ c & d \end{pmatrix}_{\text{mass}} \cdot \begin{pmatrix} 1 & Z_2 \\ Y_2 & 1 + Y_2 Z_2 \end{pmatrix}^{-1} \tag{1}$$

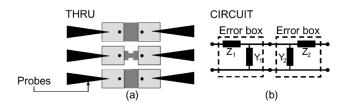

where  $(\{a,b\},\{c,d\})_{\mathrm{meas}}$  is the (known) [ABCD] matrix obtained from the measured  $S_{ij}$ ,  $(\{a,b\},\{c,d\})_{\mathrm{DUT}}$  is the (unknown) [ABCD] matrix of the DUT, the other two matrices are the [ABCD] matrices of the two error boxes shown in Fig. 2(b)  $(P_1 \text{ and } P_2)$ , and  $Y_i$  and  $Z_i$  (with i=1,2) are the parameters used to describe each parasitic box. To obtain these parameters, we used "thru", "short" and "open" calibration structures [Fig. 3(a) shows a "thru"]. For example, for a thru calibration structure, the following equation can be written:

$$\begin{pmatrix} a & b \\ c & d \end{pmatrix}_{\text{THRU}} = \begin{pmatrix} 1 + Y_1 Z_1 & Z_1 \\ Y_1 & 1 \end{pmatrix} \cdot \begin{pmatrix} 1 & Z_2 \\ Y_2 & 1 + Y_2 Z_2 \end{pmatrix}.$$

Similar equations can be written for the other two types of calibration structures. We measured the S-parameters of thru,

Fig. 3. (a) Schematics of a "thru" calibration structure. (b) Circuit model for the "thru."

Fig. 4. Cross-sectional view of the striplines. The spacing between the lines and the returns in the middle plane g was 50  $\mu$ m, and the line width was 10  $\mu$ m. The line lengths were 0.25, 0.5, 1, 2, and 8 mm.

open and short calibration structures, from which we obtained  $(Y_i, Z_i)$  for each port as a function of frequency, using (2) and the analogous equations for the short and open calibration structures.

Simple stripline structures of different lengths were included in this investigation to assess the quality of our de-embedded experimental data. A schematic of the cross section is shown in Fig. 4.

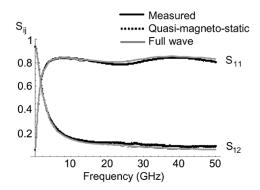

Fig. 5 compares simulations with measured S-parameters after de-embeddeding. The excellent agreement between simulations and experimental data is an indication of the good quality of our de-embedding approach.

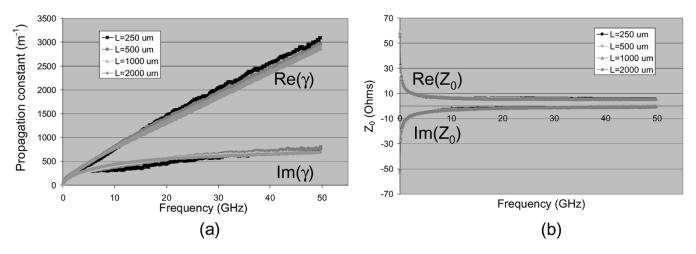

Another method to demonstrate the quality of the de-embedded experimental data is to calculate the characteristic impedance  $Z_0$  and the propagation constant  $\gamma$  from measured and de-embedded S-parameters for striplines of different lengths. Since  $Z_0$  and  $\gamma$  are length independent while S-parameters are length dependent, errors in the de-embedded S-parameters of striplines of different length would translate into different  $Z_0$  and  $\gamma$  curves. In other words, in the presence of de-embedding errors, the  $Z_0$  and  $\gamma$  curves calculated from the de-embedded S-parameters of a 1000- $\mu$ m-long stripline would be different from the ones calculated using the S-parameters of a 2000- $\mu$ m-long stripline. It is important to mention that the de-embedding equations are length dependent. Consequently, if the de-embedding is of poor quality, it is reasonable to expect that the error would be length dependent. Finally, it is also reasonable to expect that the impact of the de-embedding error would be larger for the shortest striplines than for the longer ones. The equations to obtain the characteristic impedance and propagation constant from S-parameters of striplines can be found in [3]. Fig. 6 shows the characteristic impedances and the propagation constants calculated from S-parameters of striplines of different lengths. Since all the curves are very similar, we concluded that the data were adequate for validation purposes. Based on a more detailed analysis of the results presented in Fig. 6 (not shown in this paper), we estimate the experimental error to be below 5%.

Fig. 5. Comparison between simulations and measurements after de-embedding for a 2-mm-long stripline.

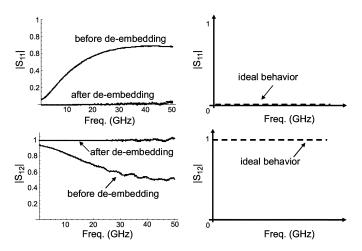

Finally, to test the self-consistency of our de-embedding approach, we used the de-embedding matrices to de-embed the calibration structures themselves. Fig. 7 shows as an example, the magnitudes of  $S_{11}$  and  $S_{22}$  of a thru calibration structure before and after de-embedding. It can be observed that before de-embedding, the measured S-parameters do not display the ideal behavior for a thru ( $S_{12}=1,S_{11}=S_{22}=0$ ) because of the important effects of the parasitics resulting from pads, vias, etc. On the contrary, the de-embedded S-parameters are very close to the ideal behavior of a thru calibration structure, which demonstrates that the de-embedding was properly implemented. Similar results were obtained for open and short calibration structures.

# III. SIMULATIONS

Simulation results derived with two different simulation tools are presented in this paper: a two-dimensional (2-D) magneto-quasi-static tool, and a full-wave tool. The magneto-quasi-static tool uses a partial element equivalent circuit (PEEC) formulation for R and L extraction, and a pure static formulation for the C extraction, where R, L, and C are, respectively, the resistance, inductance and capacitance per unit length of interconnect. In this tool, the conductors in M2 were modeled as lossy transmission lines for all structures. For structure P1, the conductors in M1 and M3 were also modeled as transmission lines. For structures OR1–OR4, which have perpendicular conductors in M1 and M3, the capacitances were extracted by replacing the perpendicular conductors by a solid metal plane, but they were removed for the R and L extractions. The Si substrate was modeled as a conductor.

The full-wave solver is a frequency-domain eigen-value method recently developed at Intel for fast full-wave modeling of large-scale interconnect structures [2]. This solver rigorously solves Maxwell's partial differential equations. It represents the original wave propagation problem into a generalized eigenvalue problem. The resulting eigen-value representation can accurately comprehend both conductor and dielectric losses, arbitrary conductor and dielectric configurations, and arbitrary materials. The wave propagation characteristics along the longitudinal direction are explicitly introduced into the modeling formulation to rigorously reduce the discretization of three-dimensional (3-D) spaces to the transverse cross section only, which significantly reduces the computational complexity. A

Fig. 6. (a) Propagation constants and (b) characteristic impedances calculated from measured and de-embedded S-parameters of striplines of different lengths.

Fig. 7. Magnitude of the S-parameters of a thru calibration structure before and after de-embedding. For reference, the behavior of an ideal thru structure is shown on the two figures to the left.

mode-matching technique applicable to lossy system is developed to solve large-scale 3-D problems by using 2-D-like CPU time and memory. For structures OR1–OR4, unlike the 2-D magneto-quasi-static tool, all perpendicular conductors in M1 and M3 are rigorously modeled. A more detailed description can be found in [2].

# IV. RESULTS AND DISCUSSION

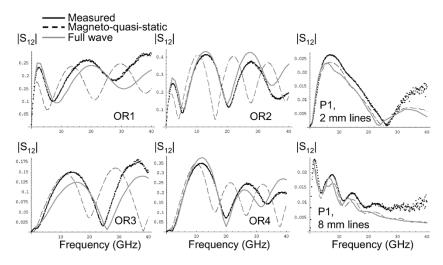

Fig. 8 compares the magnitude of  $S_{12}$  obtained with the magneto-quasi-static and the full-wave tools, to the de-embedded experimental results, as a function of frequency. From Fig. 8, the following conclusions can be made.

- There is an excellent agreement between both simulation tools and experiments for structures with parallel conductors in M1 and M3.

- 2) There is a significant frequency shift, in the range of 2–7 GHz, between the magneto-quasi-static simulations and the experiments for structures with perpendicular conductors in M1 and M3. On the contrary, an excellent agreement is observed between the full-wave results and the experiments.

3) The crosstalk noise level is an order of magnitude larger in the presence of perpendicular interconnects than in the presence of parallel interconnects in M1 and M3.

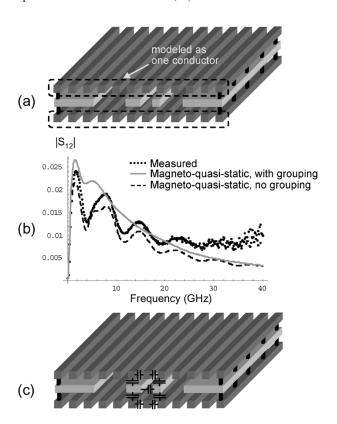

The very good agreement between the magneto-quasi-static tool and experiments at tens of gigahertz is suggesting that the magneto-static approximation holds true for structures with parallel returns in the frequency range of interest in this paper. However, it is of interest to note that the same 2-D parallel structure when simulated using the concept of electrical grouping illustrated in Fig. 9(a) (a set of conductors electrically shorted at the ends and replaced by an effective impedance), which is typically done by designers to reduce the matrix size and make the problem size more comprehensible, can show appreciable differences with measurements as illustrated in Fig. 9(b). The discrepancy can be easily explained as loss of critical information in the form of a dominant capacitive coupling not captured due to the grouping as shown in Fig. 9(c).

For the structures with perpendicular conductors in M1 and M3, only the full-wave tool accurately captures the experimental data, while the magneto-quasi-static results are affected by a significant frequency shift. It is relevant to mention that frequency shifts translate to delays in the time domain. It is also interesting to note that the frequency shift becomes significant at frequencies above 10 GHz, which contributes substantial Fourier content to typical 1–3 GHz digital signals. Consequently, for present and future clock speeds, an improper characterization of structures with perpendicular conductors could have adverse implications on timing, clock, and signal integrity assessments.

In addition, Fig. 8 shows that the amount of crosstalk strongly depends on frequency in a nonmonotonic manner, and suggests that special care should be taken when performing analysis of crosstalk at a single frequency. To demonstrate this point, we simulate an on-die bus structure with a victim, multiple aggressors, and realistic nonlinear drivers and receivers. The interconnect models are extracted using the two methodologies described in the "simulation" section and a third methodology that models the interconnects as distributed lumped R, L, and C elements whose values are extracted at a frequency corresponding to 0.3/rise time of the input excitation. Fig. 10 shows the comparison in the time domain for the noise in the victim

Fig. 8. Measured  $|S_{12}|$  as a function of frequency for structures with perpendicular conductors in M1 and M3 (OR1, OR2, OR3, and OR4) and for structures with parallel conductors in M1 and M3 (P1).

Fig. 9. (a) Two-dimensional parallel structures with upper and lower conductors electrically grouped. (b) The solid curve shows the discrepancy introduced by the grouping. (c) The dominant capacitive coupling is ignored on grouping, resulting in the discrepancy.

line simulated using the three models. It is clearly evident that the noise peak could be easily over or underestimated depending on the frequency of extraction for the distributed lumped model. A 75% overestimation in the noise peak is observed for the example considered when the single frequency extraction model is used.

It is interesting to note that the values of  $S_{12}$  of P1 are an order of magnitude smaller than those of structures OR, which is expected since the parallel conductors in M1 and M3 of P1 are more efficient current return paths than the perpendicular

Fig. 10. (a) Bus structure with orthogonal layers. (b) The solid black curve shows the discrepancy introduced by the single frequency extraction.

conductors in M1 and M3 of structures OR. Finally, the magnitude of the disagreement between the static results and experimental data was found to be significant for all the OR structures, which have different relative inductive and capacitive coupling strengths. A possible cause of the observed discrepancies between the static simulations and the experiments could be the decoupled model of E and H used in the magneto-quasi-static tools, and additional contributions could also arise from the 3-D nature of the structure at hand.

# V. SUMMARY AND CONCLUSION

We described an experimental approach that provides accurate high-frequency S-parameters, which enabled us to identify the strengths and limitations of two simulation tools that represent two common cases in this field: a 2-D magneto-quasi-static

and a 3-D full-wave tool. We found that both types of simulators can accurately capture the response of structures with parallel conductors. On the contrary, in the presence of relevant conductors that run perpendicular to signal lines, only the full-wave tool provided accurate results. The observed discrepancies between the static simulations and the experiments were ascribed to both the decoupled model of E and H used in the magneto-quasi-static tools and to the 3-D nature of the structure at hand.

Our validation approach made possible the identification of the strengths and weaknesses of both approaches as a function of frequency, which provides useful guidance to designers that have to balance the tradeoffs between accuracy and computation expenses for a large variety of practical situations.

# ACKNOWLEDGMENT

The authors wish to acknowledge Dr. E. Chiprout and Dr. W. Pinello for valuable discussions.

### REFERENCES

- D. M. Pozar, *Microwave Engineering*, 2nd ed. New York: Wiley, 1998.

D. Jiao, M. Mazumder, S. Chakravarty, C. Dai, M. Kobrinsky, M. Harmes, and S. List, "A novel technique for full-wave modeling of large-scale, three-dimensional, high-speed, on/off-chip, interconnect.

- large-scale three-dimensional high-speed on/off-chip interconnect structures," in *Int. Conf. Simulation Semiconductor Processes Devices*, Sep. 3–5, 2003, pp. 39–42.

- [3] W. Eisenstadt and Y. Eo, "S-parameter-based IC interconnect transmission line characterization," *IEEE Trans. Comp., Hybrids, Manufact. Technol.*, vol. 15, no. 4, pp. 483–483, Aug. 1992.

behavior of interconnects.

Mauro J. Kobrinsky received the M.S. degree in physics from the Balseiro Institute, Rio Negro, Argentina, in 1994 and the Ph.D. degree from the Materials Science and Engineering Department, Massachusetts Institute of Technology, Cambridge, MA, in 2001.

Since 2001, he has been with the Components Research Department, Intel Corporation, Hillsboro, OR, working on the development of advanced interconnects. His present areas of interest include processing, as well as electrical and mechanical

From 1992 to 1995, he was a Senior Antenna Design Engineer at Superline Microwave Pvt. Ltd., Bangalore, India. He worked as a Research Assistant

in the Electromagnetic Communication Laboratory, Penn State from 1997 to 2001. Since 2001, he has been with the Technology Computer-Aided Design (TCAD) Group at Intel Corporation, Hillsboro, OR. His research interests include application of computational electromagnetics to characterize the electromagnetic properties of interconnect structures, crosstalk and signal integrity analysis of interconnect structures, probabilistic optimization techniques (GA), and the applications of MoM and FDTD techniques to predict delay and crosstalk in interconnects.

**Dan Jiao** received the Ph.D. degree in electrical engineering from University of Illinois, Urbana-Champaign, in October 2001.

She is currently a Staff CAD Engineer in the Technology Computer-Aided Design (TCAD) Group, Intel Corporation, Hillsboro, OR. She has authored or coauthored two book chapters and over 50 papers in refereed journals and international conferences. Her current research interests include computational and applied electromagnetics, high-frequency VLSI CAD, fast numerical methods, fast time domain

analysis, advanced packaging, submicron semiconductor device design and analysis, scattering and antenna analysis, microwave and millimeter wave circuits, wireless communication, and bioelectromagnetics.

Dr. Jiao was the winner of the 2000 Raj Mittra Outstanding Research Award bestowed by the University of Illinois at Urbana-Champaign. In 2002, she was bestowed by Intel Components Research the Intel Hero Award for the timely and accurate two- and three- dimensional full-wave simulations. She also won a number of Divisional Achievement Awards bestowed by Intel Logic Technology Development and Technology Computer Aided Design for the development of innovative full-wave solvers and BroadSpice modeling/simulation capability for designing high-speed microprocessors, packages, and circuit boards. She served as the reviewer for the IEEE TRANSACTIONS ON ANTENNAS AND PROPAGATION, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNOLOGY, *Radio Science*, IEEE TRANSACTIONS ON ADVANCED PACKAGING, *Microwave And Optical Technology Letters*, IEEE ANTENNAS AND WIRELESS PROPAGATION LETTERS, IEEE International Conference on Computer Aided Design, and International Conference on Simulation of Semiconductor Processes and Devices.

Michael C. Harmes is a Senior Technician in Intel's Components Research Department, Hillsboro, OR, and has been with the Intel Corporation for 20 years. His work has focused in the area of electrical characterization of ICs using testers and test systems, and has included RAMS, DRAMS, microcontrollers, PLDs, microprocessors, and telecommunication products. His present responsibilities include development and support of novel electrical testing for advanced interconnects.

**Scott List** received the Ph.D. degree in applied physics from Stanford University, Stanford, CA.

He is currently with Intel at the Interuniversity MicroElectronics Center (IMEC), Leuven, Belgium. From 1998 to 2004, he was a Manager of interconnects research in the Components Research Department working on a variety of back-end areas including 3-D wafer stacking, die-package interactions, and high-frequency measurements and simulations. He spent eight years at Texas Instruments and two years at Los Alamos National

Laboratory, Los Alamos, NM, before joining Intel working on low-k dielectrics, shallow junction transistors, HgCdTe infrared detectors, and high-temperature superconductors. He is a coauthor of over 80 publications and 30 patent applications.

Mohiuddin Mazumder received the B.S. degree in electrical engineering from Bangladesh University of Engineering and Technology, Dhaka, in 1989, the M.S. degree in electrical engineering from New Mexico State University, Las Cruces, in 1992, and the Ph.D. degree in applied physics from Yale University, New Haven, CT, in 1996.

He then joined the Technology Computer-Aided Design (TCAD) Group, Intel Corporation, Santa Clara, CA. He has been working on high-frequency interconnect modeling issues in chip, package, and

board designs. He has developed an on-chip inductance simulation methodology at Intel. He worked with all major microprocessor design groups to develop on-chip inductance design guidelines to avoid inductance issues. He is interested in developing integrated CAD solutions for signal integrity analysis.