## Homework 2

## ECE 559: MOS VLSI Design (Fall 2009)

## ECE Department, Purdue University

## Assigned: 24-Sep-2009

Due: 06-Oct-2009

**Important:** Please turn-in all of your codes along with the waveforms (when necessary) during submission of your solution. You may be asked to provide the soft copy of your codes by email if such need arises.

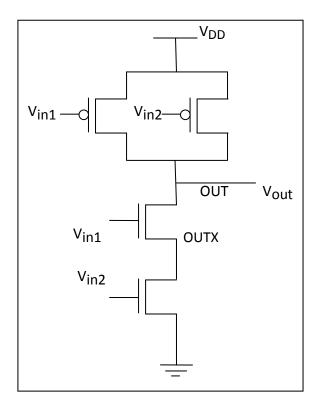

**Problem 1:** Consider a 2-input NAND gate as below.

- a) Assume the following two different cases of input transitions

- 1)  $V_{in1}$  is fixed at logic '1' and  $V_{in2}$  is making transition from  $0 \rightarrow 1$ .

- 2)  $V_{in2}$  is fixed at logic '1' and  $V_{in1}$  is making transition from  $0 \rightarrow 1$ .

Which case will incur a higher falling delay at the output? Explain clearly the reason.

**b)** Do a SPICE simulation with the libraries that you have used in Tutorial 2, i.e., *tsmc25N* and *tsmc25P* to confirm the result. Assume the following parameters

L=240nm, W<sub>p</sub> =1250nm, W<sub>n</sub> =450nm, V<sub>DD</sub> = 2.5 V.

Also, connect a 20f F capacitance at both the nodes OUT and OUTX.

**Problem 2:** Consider the same 2-input NAND gate as in the problem 1. Assume that the substrates for all the PMOSs and NMOSs are connected to V<sub>DD</sub> and ground, respectively.

a) You do not need to consider the capacitances at the nodes *OUT* and *OUTX* for this part. Assume the following.

| V <sub>DD</sub> = 1 V                    | V <sub>in1</sub> = V <sub>in2</sub> = 0.5 V |                       |

|------------------------------------------|---------------------------------------------|-----------------------|

| $K_{p}' = \mu_{p}C_{OX} = 30e-6 A/V^{2}$ | $K_{n}' = \mu_{n}C_{0x} = 60e-6 A/V^{2}$    |                       |

| V <sub>tp</sub> = -0.3 V                 | V <sub>tn</sub> = 0.3 V                     | (without body effect) |

| 2φ <sub>f</sub>   = 0.6 V                | $\gamma = 0.4 V^{0.5}$                      |                       |

| $W_p/L_p = 2$                            | $W_n/L_n = 2.$                              |                       |

Determine the output voltage, Vout

- i. Without body effect

- ii. With body effect

You may think of using *matlab* to solve your equations.

**b)** Do a SPICE simulation with the libraries that you have used in Tutorial 2, i.e., *tsmc25N* and *tsmc25P*. Assume the following parameters

L=240nm,

$$W_p = 1250nm$$

,  $W_n = 450nm$ ,  $V_{DD} = 2.5 V$ ,  $V_{in1} = V_{in2} = 1.25 V$ .

Also, connect a 20f F capacitance at both the nodes OUT and OUTX.

The body-effect is modeled in SPICE as follows.

$$\Delta V_{T,body\_effect} = k1. \left(\sqrt{2\phi_f - V_{BS}} - \sqrt{2\phi_f}\right) - k2.V_{BS}$$

where *k1* and *k2* are fitting coefficients. So if we don't want to consider the body effect, we need to make these two coefficients zero in the corresponding libraries *tsmc25N* and *tsmc25P*. The location of the library files is

\package\eda\cells\ncsu-cdk-1.5.1\local\models\hspice\public\publicModel\.

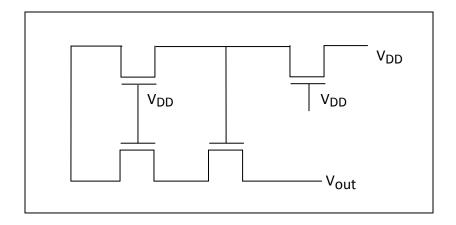

**Problem 3:** Consider a pass-transistor network as shown in the below figure. Assume the following. Assume that the substrates of all the NMOSs are connected ground.

$V_{DD} = 1 V$   $K_n' = \mu_n C_{OX} = 60e-6 A/V^2$   $V_{tn} = 0.3 V \text{ (without body effect)}$   $|2\phi_f| = 0.6 V$  $\gamma = 0.4 V^{0.5}$

$W_n/L_n = 1.$

Determine the output voltage, Vout

- i. Without body effect

- ii. With body effect

You may think of using *matlab* to solve your equations.