# ECE 559 Lab Tutorial 2

HSPICE, Nanosim, and NanoTime Simulation Introduction

# Contents

| 1 | Intro | oduction                                            | 3  |

|---|-------|-----------------------------------------------------|----|

| 2 | Cad   | lence Analog Design Environment                     | 3  |

|   | 2.1   | Launch Analog Design Environment (ADE)              | 3  |

|   | 2.2   | HSPICE Simulation Setup                             | 3  |

|   | 2.3   | Stimuli Setup                                       | 4  |

|   | 2.4   | Simulation Output Data                              | 6  |

|   | 2.5   | Viewing Simulation Results                          | 7  |

|   | 2.6   | Saving and loading States                           | 8  |

| 3 | Vari  | iable and Parametric Analysis                       | 10 |

|   | 3.1   | Create a cellview                                   | 10 |

|   | 3.2   | Launch Analog Design Environment (ADE)              | 10 |

|   | 3.3   | Setting up Additional Output for Delay Measurements | 11 |

|   | 3.4   | Variable setup                                      | 14 |

|   | 3.5   | Running Simulation                                  | 15 |

|   | 3.6   | Parametric Analysis                                 | 15 |

| 4 | Netl  | list Extraction & Running HSPICE from Command Line  | 16 |

|   | 4.1   | Extracting Netlist                                  | 16 |

|   | 4.2   | Online Documentation                                | 17 |

|   | 4.3   | Running HSPICE                                      | 17 |

|   | 4.4   | HSPICE Netlist Example                              | 18 |

|   | 4.5   | CosmosScope                                         | 20 |

| 5 | Nan   | nosim                                               | 22 |

|   | 5.1   | Online Documentation                                | 22 |

|   | 5.2   | Netlist                                             | 22 |

|   | 5.3   | Configuration File                                  | 22 |

|   | 5.4   | Running Nanosim                                     | 23 |

|   | 5.5   | Using Input Vector File                             | 24 |

|   | 5.5.  | 1 SPICE Netlist                                     | 24 |

|   | 5.5.2 | 2Command                                            | 25 |

|   | 5.6   | CosmosScope                                         | 25 |

|   | 5.7   | Delay Measurement                                   | 26 |

|   |       | 5.7.1 Command                                       | 27 |

|   |       | 5.7.2 Running Simulation                            | 27 |

|   |       | 5.7.3 Viewing SDF and PATH Files                    | 27 |

|   | 5.8   | Using Graphical User Interface                      | 28 |

| 6 | Nan   | noTime                                              | 30 |

| 6.1 | Online Documentation            | 30 |

|-----|---------------------------------|----|

| 6.2 | SPICE Netlist                   | 30 |

| 6.3 | Tech File                       | 31 |

| 6.4 | Script/Configuration File       | 32 |

| 6.5 | Command                         | 34 |

| 6.6 | Results                         | 34 |

| 6.7 | Worst Case Input Vector         | 34 |

|     | 6.7.1 Script/Configuration File | 35 |

|     | 6.7.2 SPICE File                |    |

|     | 6.7.3 Generated SPICE File      | 37 |

|     |                                 |    |

# **1** Introduction

The purpose of the second lab tutorial is to help you in simulating your inverter design that you designed in the first lab tutorial. You will use HSPICE and Nanosim to simulate your design and evaluate its performance by examining the simulation results.

Upon completion of this tutorial, you should be able to:

- Simulate your schematic using HSPICE

- Examine the results of your HSPICE simulation

- Extract a netlist from your schematic

- Simulate your schematic using Nanosim

- Examine the results of your Nanosim simulation using CosmosScope

# 2 Cadence Analog Design Environment

The Analog Design Environment is the place where all the simulations and the netlist extractions of your inverter design can be done. Here you can set up the type of simulation to be run with the appropriate input signals, run the simulation, and display the results in a graphical viewer.

### 2.1 Launch Analog Design Environment (ADE)

- If you have not opened your *InverterTest* schematic cellview, open it by selecting **File** -> **Open** from the drop down menu in the CIW. Select the *tutorial* library and make sure that you select the schematic view.

- In the schematic window, select **Tools** -> **Analog Environment** from the drop-down menu. A new window named *Virtuoso@ Analog Design Environment* appears.

- The correct design (Library, Cell, and View) to be simulated should be displayed in the figure below.

#### 2.2 HSPICE Simulation Setup

- To setup a HSPICE simulation, select **Setup** -> **Simulator/Directory/Host** from the drop down menu. A new window named *Choosing Simulator/Directory/Host* appears. Select *hspiceS* for the *Simulator*.

- The *Project Directory* field specifies where the simulation files and results are to be stored. If you need to store results in another directory or path, you can change it here. Note that results from subsequent simulation runs will overwrite the previous results

| ¥irtuoso® Analog Design E<br>Status: Ready | T=25 C Simulator: hspiceS                           | . <mark></mark>        |

|--------------------------------------------|-----------------------------------------------------|------------------------|

| Session Setup Analyses                     | Variables Outputs Simulation Results Tools          | Help                   |

| Design                                     | Analyses                                            | ÷Ę                     |

| Library tutorial<br>Cell InverterTest      | # Type Arguments Enable                             | ⊐ AC<br>■ TRAN<br>⊐ DC |

| Cell InverterTest<br>Mew schematic         |                                                     | III<br>XYZ             |

| Design Variables                           | Outputs                                             | Œ                      |

| # Name Value                               | <pre># Name/Signal/Expr Value Plot Save March</pre> |                        |

|                                            |                                                     | 8                      |

|                                            |                                                     | 8                      |

|                                            | Plotting mode: Replace =                            | to                     |

unless they are to be stored in a different location. For this tutorial, just use the default path. Click **OK** to finish.

- The schematic window will refresh and the schematic should reappear in a few seconds. Now in the upper right corner of the *Analog Design Environment* window, the simulator should be *hspiceS*.

- To setup the type of analysis to be performed (transient, DC, AC etc). Select **Analyses** -> **Choose** or click the *Choose Analyses* icon on the right. A new window appears. For this tutorial, we will perform a transient analysis that starts from 0ns to 30ns in 1ns steps (Type in '30n' instead of '30ns'). Select *tran* for *Analysis* and enter the corresponding values. Click **OK** when done.

- Now in the *Analog Circuit Design Environment* window, the *Analyses* field should now display the type of analysis to be performed with the corresponding arguments.

### 2.3 Stimuli Setup

• To setup stimulus or input signals, select **Setup** -> **Stimulus** -> **Edit Analog**. In the new window that appears, click on *graphical* and then click OK.

- A new window named *Setup Analog Stimuli* appears. Click on *Inputs* for *Stimulus Type* and select an input signal from the list below. In this tutorial, there are two inputs In<1> and In<0>. Click on In<0> to start entering the stimulus.

- Function: Pulse

- Type: Voltage

- Voltage 1: 0.0

- Voltage 2: 2.5

- Delay time: 1n

- Rise time: 1n

- Fall time: 1n

- Pulse Width: 10n

- Period: 20n

After you have entered all the parameters, check on the '**enabled**' option to turn on the input signal. Click on the **Change** or **Apply** button to set the values. Do not click **OK** yet.

| Setup Analog Stimuli   | _ <b>_ _</b> ×                                                 |

|------------------------|----------------------------------------------------------------|

| OK Cancel Apply        | Help                                                           |

| Stimulus Type 🔶 Inputs | ◇ Global Sources                                               |

|                        | pulse "Voltage 1"=0.0 "Voltag<br>pulse "Voltage 1"=0.0 "Voltag |

|                        | Change                                                         |

| Enabled 📕 Function     | pulse = Type Voltage =                                         |

| AC magnitude           |                                                                |

| AC phase               | Ĭ.                                                             |

| Voltage 1              | 0. Q <u>í</u>                                                  |

| Voltage 2              | 2.5                                                            |

| Delay time             | lr <u>i</u>                                                    |

| Rise time              | 1n <u>í</u>                                                    |

| Fall time              | 1n <u>í</u>                                                    |

| Pulse width            | 10r <u>i</u>                                                   |

| Period                 | 20m <u>í</u>                                                   |

| DC source              | Ĭ                                                              |

- Repeat entering the stimulus for In<1>.

- Now, you need to specify the voltages of the global sources (Vdd). Click on *Global Sources* and a new list should appear. Select *dc* for *Function*, *Voltage* for *Type* and enter 2.5v for *DC voltage*. Check on the 'enabled' option to turn on the voltage source and click Change or Apply to set the values. Click OK to finish setting up stimuli.

| 🗙 Setu | p Analog | Stimuli    |                           |          |           |

|--------|----------|------------|---------------------------|----------|-----------|

| ОК     | Cancel   | Apply      |                           |          | Help      |

| Stimul | us Type  | ♦ Inputs   | 🔶 Global So               | urces    |           |

| ON V   | rdd! /gn | d! Voltage | e de "DC <del>v</del> olt | age"=2.5 | V         |

|        |          |            |                           |          |           |

|        |          |            | Change                    |          |           |

| Enable | d 📕      | Function   | dc =                      | Туре     | Voltage 🗆 |

| AC ma  | gnitude  |            | Ĭ.                        |          |           |

| AC pha | se       |            | Ĭ.                        |          |           |

| DC vol | tage     |            | 2.5 <b>v</b>              |          |           |

### 2.4 Simulation Output Data

- The data obtained from the simulation can be saved, plotted or marched. The saved data will be written to disk in the *Project Directory* specified above. The plotted set of data can be plotted in a Waveform window. The marched set of data will be plotted in the Marching Waveform window during simulation.

- To add nodes and terminals to the saved, plotted, or marched set, select Outputs -> To Be

-> Select On Schematic. In the schematic window, choose one or more nodes or terminals. When selecting, click on the square pin symbols to choose currents and click on wires to choose voltages. For this tutorial, select the input and output wires (bus). Note that if you select a bus, three nodes will appear e.g. In<0:1>, In<0> and In<1>.

- Although it is not recommended, it is possible to save all node voltages and terminal currents of the simulation. To do so, select **Outputs** -> **Save all**. In the window that appears, check the box next to *Select all node voltages* and click **OK**. Note that this may create unnecessary large data files, especially for a large design. To undo the save all function, choose **Outputs** -> **Save all** and uncheck the box next to *Select all node voltages*.

| Virtuoso® Analog Design I<br>Status: Ready        | T=25 C Simulator: hspices                                                                                                                                | <u>   ×</u><br>3 3 |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Session Setup Analyses                            | Variables Outputs Simulation Results Tools                                                                                                               | Help               |

| Design                                            | Analyses                                                                                                                                                 | ᠂᠊ᠺᢩ               |

| Library tutorial                                  | # Type Arguments Enable                                                                                                                                  | ⊐ AC<br>E TRAN     |

| <b>Cell</b> InverterTest<br><b>View</b> schematic | 1 tran 0 30n 1n yes                                                                                                                                      |                    |

| Design Variables                                  | Outputs                                                                                                                                                  |                    |

| # Name Value                                      | <pre># Name/Signal/Expr Value Plot Save March</pre>                                                                                                      |                    |

|                                                   | 1         In<0>         yes         allv no           2         In<1>         yes         allv no           3         Out<0>         yes         allv no | <u>م</u>           |

|                                                   | 4 Out<1> yes allv no                                                                                                                                     | 8                  |

|                                                   | Plotting mode: Replace =                                                                                                                                 | 1                  |

- To delete a node or terminal from the saved, plotted, or marched set, select **Outputs** -> **Setup**. In the window that appears, double-click on the node or terminal in the *Table Of Outputs* list box and check the appropriate *Will Be* boxes. Click **Change** to update the changes. Click **OK** when done.

- To delete a node from all three sets, highlight the node in the simulation window and choose **Outputs** -> **Setup** or click the *Delete* icon on the right.

- To run the simulation, select **Simulation** -> **Run** or click the *Run Simulation* icon on the right. The CIW will display the status and the results of the simulation. Errors or warnings will be displayed here if found.

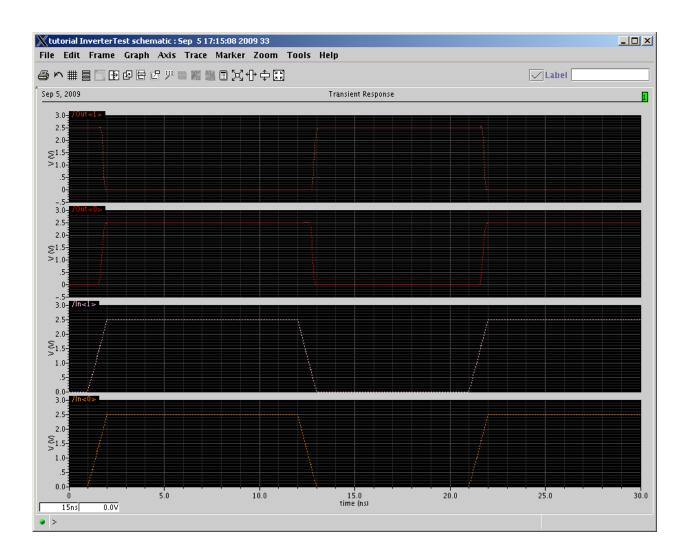

### 2.5 Viewing Simulation Results

- After a successful simulation, the plotted results can be displayed by selecting **Tools** -> **Results Browser**. A new window appears. Make sure the specified project directory is corresponding to the schematic (eg : ./simulation/InverterTest/hspiceS/schematic/psf). Double click on **timesweep** in the left subwindow. A list of nodes appears in the right subwindow.

- Since we would like to display the transient waveform, **right click** on *in\_1* and select the *New Win* option. The waveform can also be seen by double clicking on the signal.

| 💥 Results Browser                                                                |                                                                                                                                                                                  |           |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <u>F</u> ile <u>S</u> ettings <u>T</u> ools <u>H</u> elp                         |                                                                                                                                                                                  |           |

| 🚅 🖄 🖩 🖥 🚱 🛄 🖻                                                                    | F                                                                                                                                                                                | Replace 🔻 |

| Location ./ cadence/ simulation                                                  | /InverterTest/hspiceS/schematic/psf                                                                                                                                              | •         |

| <pre>/home/min/a/royk/cadence/si element opBegin timeSweep opEnd variables</pre> | gnd!         i(vin_0)         i(vin_1)         i(vvdd!)         in_0         in_1         internal<0>         internal<1>         net38         out_0         out_1         vdd! |           |

| >                                                                                |                                                                                                                                                                                  | cādence   |

- The waveform of the *In\_1* signal is displayed in the *Waveform Window* that appears. To display more signals in the same waveform window **right click** on the signal and select the *Append* option. To view the waveform in a new subwindow select the *New Subwin* option.

- To display the waveform of the *Out* signal, return to the Results Browser and do the above steps for the output signals. The waveform will be plotted in the *Waveform Window*.

- The two waveforms are displayed on the same axis and should be inverted with respect to each other. To split them into separate axis, click on the *Strip Chart Mode* icon on the top. Clicking on the icon again combines the waveforms into the same axis.

- Note that not all of the functions under **Results** and **Tools** work with the HSPICE interface.

### 2.6 Saving and Loading States

• Saving states allow you to save and restore all or part of the simulation setup so that lot of steps can be saved when setting up the simulation (for a similar simulation run). To do this, select **Session -> Save State**.

- In the new window that appears, choose a name for the simulation setup to be saved, and select what items to save. Click **OK** to save.

- Close Analog Design Environment and restart it by selecting Tools -> Analog Environment menu in the schematic window. To retrieve and restore previously saved setup first select the correct simulator (hspiceS) by Setup -> Simulator/Directory/Host, then select Session -> Load State. A new window appears. Choose the desired value in the *Library*, *Cell* and *Simulator* fields.

- *State Name* specifies all the saved states for the cell and simulator combination that you specified. Choose the *What to Load* options you need and click **OK**.

# 3 Variable and Parametric Analysis

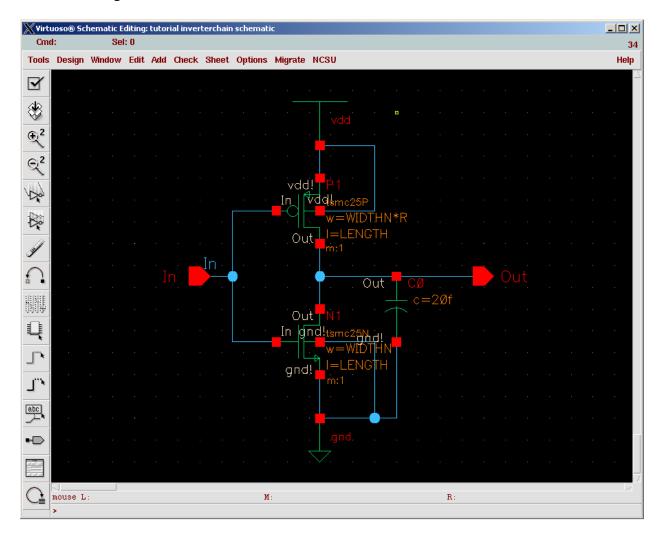

## 3.1 Create a cellview

Create a cellview as in the figure with following parameters. Note that the sizes of the transistors are specified using variables.

- PMOS width : WIDTHN\*R

- PMOS length : LENGTH

- NMOS width : WIDTHN

- NMOS length : LENGTH

## 3.2 Launch Analog Design Environment (ADE)

- Launch Analog Design Environment **Tools -> Analog Environment**.

- In ADE, Setup -> Simulator/Directory/Host: select *hspiceS* for the *Simulator*.

- In ADE, **Setup** -> **Stimulus** -> **Edit Analog**. In the new window that appears, click on *graphical* and then click OK.

- A new window named *Setup Analog Stimuli* appears. Click on *Inputs* for *Stimulus Type* and select an input signal from the list below. Click on In to start entering the stimulus.

- Function: Pulse

- Type: Voltage

- Voltage 1: 0.0

- Voltage 2: 2.5

- Delay time: 1n

- Rise time: 1n

- Fall time: 1n

- Pulse Width: 10n

- Period: 20n

After you have entered all the parameters, check on the '**enabled**' option to turn on the input signal. Click on the **Change** or **Apply** button to set the values. Do not click **OK** yet.

- Now, you need to specify the voltages of the global sources (Vdd). Click on *Global Sources* and a new list should appear. Select *dc* for *Function*, *Voltage* for *Type* and enter 2.5v for *DC voltage*. Check on the 'enabled' option to turn on the voltage source and click Change or Apply to set the values. Click OK to finish setting up stimuli.

- To setup the type of analysis to be performed (transient, DC, AC etc). Select **Analyses** -> **Choose** or click the *Choose Analyses* icon on the right. A new window appears. For this tutorial, we will perform a transient analysis that starts from 0ns to 30ns in 1ns steps (Type in '30n' instead of '30ns'). Select *tran* for *Analysis* and enter the corresponding values. Click **OK** when done.

- Now in the *Analog Circuit Design Environment* window, the *Analyses* field should now display the type of analysis to be performed with the corresponding arguments.

- To add nodes and terminals to the saved, plotted, or marched set, select Outputs -> To Be

... -> Select On Schematic. In the schematic window, choose one or more nodes or terminals. When selecting, click on the square pin symbols to choose currents and click on wires to choose voltages. For this tutorial, select the input and output wires.

### 3.3 Setting up Additional Output for Delay Measurements

- In ADE, **Outputs** -> **Setup**

- In *Setting Outputs* window, Click **Calculator Open**

- Click *vt* button in *Calculator*,

- Click *out* wire in schematic window,

- Click *in* wire in schematic window,

• Select **delay** from the functions in the sub-window on the lower right corner. The window changes into the figure shown. Please make sure that the **Signal1** is corresponding to VT("/In") and **Signal 2** is corresponding to VT("/Out"). Change the other values as shown. Then click on the ">>>" button.

| XCalculator                                      |                                   | × |

|--------------------------------------------------|-----------------------------------|---|

| Window Tools Memories Con                        | nst Options Help                  |   |

| no data set                                      |                                   |   |

| Selection choices                                |                                   |   |

| ✓ clip graph selection                           | tran ac dc swept_dc info noise rf |   |

| off $\bigcirc$ family $\bigcirc$ wave $\bigcirc$ | vt  it                            |   |

| VT('/In')                                        |                                   |   |

|                                                  | delay                             |   |

| Append 🔻 📈 III                                   |                                   |   |

| Clear Undo Eval                                  | Signal1 VT("/In")                 |   |

| 1/x eex Cist Enter                               | Signal2 VT("/Out")                |   |

| + 7 8 9                                          | Threshold Value 1 1.25            |   |

| - 4 5 6                                          | Edge Number 1 1                   |   |

| x 1 2 3                                          | Edge Type 1 rising 👻              |   |

| / 0 . +/-                                        | Periodicity 1                     |   |

|                                                  |                                   |   |

|                                                  | <<< Ok Cancel Apply Defaults >>>  |   |

| >                                                | [cādenc                           | e |

- This will bring the next parameters to be entered as in the next figure. Complete the values as shown. Click **OK** and you will see the following screen with the formula depicted. What we have done here is generated an expression to measure the delay from the first rising edge of the input to the first falling edge of the output. The threshold voltage levels have been given as 1.25 V for both the input and the output signals (as filled in *Threshold Value 1* and *Threshold Value 2* boxes).

- In Setting Outputs window, Click Get Expression

- Name this output as *delay1* and click **Add**

- Similarly, add one more output *delay2* which measures the delay from the 1<sup>st</sup> falling edge of the input to the 1<sup>st</sup> rising edge of the output.

| Window Tools Memories Const Options Help                   |          |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|--|

|                                                            |          |  |  |  |  |  |  |  |  |  |

| no data set                                                |          |  |  |  |  |  |  |  |  |  |

| Selection choices                                          |          |  |  |  |  |  |  |  |  |  |

| Let clip graph selection tran at dt swept_dt info noise rf |          |  |  |  |  |  |  |  |  |  |

| off family wave vt it                                      |          |  |  |  |  |  |  |  |  |  |

|                                                            |          |  |  |  |  |  |  |  |  |  |

| VT('/In')                                                  | •        |  |  |  |  |  |  |  |  |  |

| delav                                                      |          |  |  |  |  |  |  |  |  |  |

| Append 🔻 📈 III                                             |          |  |  |  |  |  |  |  |  |  |

| Clear Undo Eval Threshold Value 2 1.25                     |          |  |  |  |  |  |  |  |  |  |

| 1/x eex Clst Enter Edge Number 2 1                         |          |  |  |  |  |  |  |  |  |  |

|                                                            | -        |  |  |  |  |  |  |  |  |  |

|                                                            | -        |  |  |  |  |  |  |  |  |  |

| - 4 5 6 Periodicity 2 1                                    |          |  |  |  |  |  |  |  |  |  |

| x 1 2 3 Number of occurrences single                       | -        |  |  |  |  |  |  |  |  |  |

| / 0 . +/-                                                  |          |  |  |  |  |  |  |  |  |  |

| Plot/print vs. trigger                                     |          |  |  |  |  |  |  |  |  |  |

|                                                            |          |  |  |  |  |  |  |  |  |  |

| <<< Ok Cancel Apply Defa                                   | ults >>> |  |  |  |  |  |  |  |  |  |

| >                                                          | cādenco  |  |  |  |  |  |  |  |  |  |

|                                                            | Leadence |  |  |  |  |  |  |  |  |  |

| Window Tools Memories Const Options Help                                    |           |

|-----------------------------------------------------------------------------|-----------|

| no data set                                                                 |           |

| _ Selection choices                                                         |           |

| ✓ clip graph selection tran ac dc swept_dc info noise rf                    |           |

| dan at at sneptat mis nose n                                                |           |

| off family wave vt it                                                       |           |

| delay(\/T('/In') 1.25 1 "rising" \/T('/Out") 1.25 1 "falling" 0 0 nil nil ) | -         |

|                                                                             | <b>`</b>  |

| Append 🔻 💹 III                                                              |           |

| Clear Undo Eval Threshold Value 2 1.25                                      |           |

| 1/w cow Clst Enter Edge Number 2 1                                          |           |

|                                                                             |           |

| + 7 8 9 Edge Type 2 falling                                                 | <b>•</b>  |

| - 4 5 6 Periodicity 2 1                                                     |           |

| x     1     2     3       Number of occurrences     single                  | <b></b>   |

| / 0 . +/-                                                                   |           |

| Plot/print vs. trigger                                                      | <b>•</b>  |

|                                                                             |           |

| <<< Ok Cancel Apply Defa                                                    | aults >>> |

|                                                                             |           |

| >                                                                           | cādence   |

| Setting Out | puts Virtuoso® Analog Design Environment ( | 2)                                                                                                                                                                                                                  |                  |           |            |      | <u>- 🗆 ×</u> |

|-------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|------------|------|--------------|

| OK Canc     | el Apply                                   |                                                                                                                                                                                                                     |                  |           |            |      | Help         |

|             | Selected Output                            |                                                                                                                                                                                                                     | Table            | Of Output | s          |      |              |

| Name (opt.) | delay2                                     | #                                                                                                                                                                                                                   | Name/Signal/Expr | Value     | Plot       | Save | March        |

| Expression  | "/Out") 1.25 1 "rising" 0 0 nil nil)       | $\frac{1}{2}$                                                                                                                                                                                                       | In<br>Out        |           | yes<br>ves |      |              |

| Calculator  | Open Get Expression Close                  | Acted Output     Table Of Outputs       # Name/Signal/Expr     Value       1.25 1 "rising" 0 0 nil nil)[     1       1     In       2     Out       2     Out       3     delay1       4     delay2       2     yes |                  |           |            |      |              |

| Will Be     | Plotted/Evaluated                          | -                                                                                                                                                                                                                   | uctay2           |           | y00        |      |              |

| Add De      | lete Change Next New Expression            |                                                                                                                                                                                                                     |                  |           |            |      |              |

• In Setting Outputs window, Click OK.

# 3.4 Variable setup

- In ADE, Variables -> Copy from Cellview

- Variables will appear in ADE window.

- Double click the variables to set the values as the next figure.

| S            | tatus: Rea            | ady                |                  |                           |       |        |        |       | T=25 (  | : Sim                    | ulator       | : hspiceS | 35             |

|--------------|-----------------------|--------------------|------------------|---------------------------|-------|--------|--------|-------|---------|--------------------------|--------------|-----------|----------------|

| Ses          | ssion Set             | up Analyses        | Varia            | bles                      | Outp  | uts Si | imulat | ion   | Results | s Too                    | ls           |           | Help           |

|              | De                    | sign               |                  |                           |       |        | An     | alys  | es      |                          |              |           | ۲Ţ             |

| Libr         | <b>ary</b> tuto:      | rial               | #                | Тур                       | e     |        |        |       |         |                          |              | Enable    | ⊐ AC<br>E TRAN |

| Cell<br>Vie\ |                       | rterchain<br>matic | 1                | tra                       | n     | 0      | 3      | 30n   | 1n      |                          |              | yes       | JDC            |

|              | Design \              | /ariables          |                  |                           |       |        | 0      | utpu  | its     |                          |              |           |                |

| #            | Name                  | Value              | #                | Nam                       | e/Sig | nal/E> | φr     | ۷     | alue    | Plot                     | Save         | March     |                |

| 1<br>2<br>3  | WIDTHN<br>R<br>LENGTH | 300n<br>1<br>240n  | 1<br>2<br>3<br>4 | In<br>Out<br>del:<br>del: |       |        |        |       |         | yes<br>yes<br>yes<br>yes | allv<br>allv |           | 8              |

|              |                       |                    |                  |                           |       |        | Plo    | ottin | g mode  | :                        | Replac       | :e =      |                |

# 3.5 Running Simulation

• Run the simulation and note that there are delay measurement results beside the output names delay1 and delay2.

| Virtuoso® Analog Design Environment (2)<br>Status: Ready T=25 C Simulator: hspice S |                                                         |       |  |  |

|-------------------------------------------------------------------------------------|---------------------------------------------------------|-------|--|--|

| Session Setup Analy                                                                 | ses Variables Outputs Simulation Results Tools          | Help  |  |  |

| Design                                                                              | Analyses                                                | ٠Ę    |  |  |

| Library tutorial                                                                    | # Type Arguments Enabl                                  | TRAN  |  |  |

| Cell inverterchair                                                                  | n 1 tran 0 30n 1n yes                                   |       |  |  |

| <b>View</b> schematic                                                               |                                                         | x y z |  |  |

| Design Variables                                                                    | Outputs                                                 | Ē     |  |  |

| # Name Value                                                                        | <pre># Name/Signal/Expr Value Plot Save March</pre>     |       |  |  |

| 1 WIDTHN 300n                                                                       | 1 In yes ally no                                        | _     |  |  |

| 2 R 1<br>3 LENGTH 240n                                                              | 2 Out yes allv no<br>3 delay1 180.1p<br>4 delay2 465.9p | 8     |  |  |

|                                                                                     |                                                         | 1     |  |  |

|                                                                                     | Plotting mode: Replace =                                | t.    |  |  |

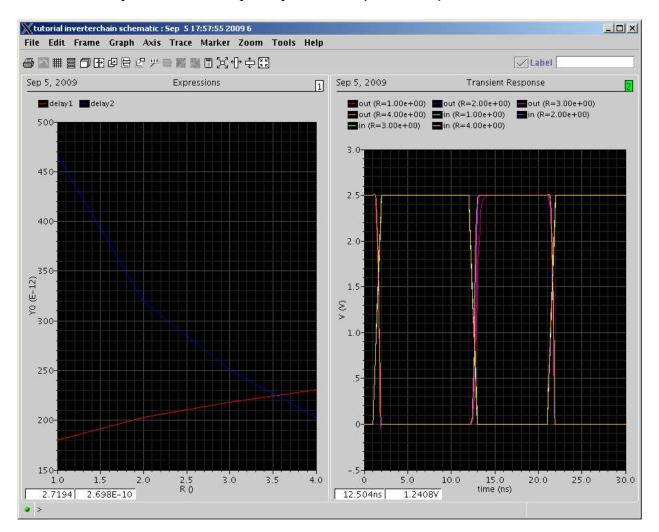

# 3.6 Parametric Analysis

- In ADE, Tools -> Parametric Analysis

- Complete the sweep variables as in the following figure.

| Parametric Analysis - hspice5(1): tutorial inverterchain schematic |                  |               |             |    |                     |          |   |

|--------------------------------------------------------------------|------------------|---------------|-------------|----|---------------------|----------|---|

| Tool Sweep                                                         | ) Setup Analysis |               |             |    |                     | Help     | 7 |

|                                                                    |                  |               |             |    |                     |          |   |

| Sweep 1                                                            |                  | Variable Name | <b>F</b> ř. | [  | Add Specification = |          |   |

| Range Type                                                         | From/To 🖃        | From          | 1           | То | 4                   | Salaat 🗔 |   |

| Step Control                                                       | Linear Steps =   | Step Size     | 1           | [  |                     | Select _ |   |

|                                                                    |                  |               |             |    |                     |          |   |

|                                                                    |                  |               |             |    |                     |          |   |

- In Parametric Analysis window, Analysis -> Start

- *Waveform window* will appear with two plots. The right side shows the waveforms of *In* and *Out* pins. The left side plot represents *delay1* and *delay2* values for different *R*.

# 4 Netlist Extraction & Running HSPICE from Command Line

### 4.1 Extracting Netlist

A netlist file describes the system or circuit to be simulated. The file specifies the components or instances in the circuit, how the circuit is connected together, what type of simulation is to be run, what inputs are supplied and what outputs are to be obtained.

• To extract a HSPICE format netlist, the procedures are identical to the ones required to setup a HSPICE simulation in *Analog Design Environment*, except that instead of running the simulation, a netlist is extracted. This is because although it is transparent to

the user, a netlist is generated before the HSPICE simulation is run under the Analog Design Environment.

- If a successful simulation run has been done, the netlist is already created and can be readily viewed by selecting **Simulation -> Netlist -> Display Final**.

- If the HSPICE simulation has not been set up or run for the inverter schematic, use the *Analog Design Environment* to setup the HSPICE simulation as done in the previous section, but do not run the simulation. If you have saved states, you could use them here to simplify the set up process.

- Select **Simulation** -> **Netlist** -> **Create Final**. The CIW will display the status and the results of the netlist extraction process. Errors or warnings will be displayed here if found.

- If the netlist extraction is successful, a new window displaying the extracted netlist appears. The netlist itself is named hspiceFinal and is stored in the *project directory* specified in the *Analog Design Environment* (~/cadence/simulation/InverterTest/hspiceS/schematic/netlist). You can use any text editor to view or edit the netlist.

- If you are familiar with HSPICE/SPICE, you should be able to recognize all of the statements and elements in the netlist.

#### 4.2 Online Documentation

- To access the online documentation, type grid hspice -help in a terminal window.

- In the online documentation, you can get the *pdf* copy of different manuals by clicking the *pdf* link at the bottom of the right frame.

### 4.3 Running HSPICE

- Before running HSPICE in command line, open the input file (hspiceFinal) with a text editor and do the following first.

- Find the lines that include following and delete it.

```

.OPTION INGOLD=2 ARTIST=2 PSF=2

+ PROBE=0

```

- Add following line: .OPTION POST

*.option post* instructs HSPICE to write an output file ending in .tr0 containing the simulation waveforms.

[If you don't like to edit the netlist file after generation, you can choose *Simulation - Options – Analog* menu in *Analog Design Environment* window and set POST option to '1' before the generation of the final netlist. Then, you can use the hspiceFinal in your HSPICE simulation without modification. Note that it's only for the case of command line HSPICE simulation]

• Now that you have obtained a netlist, you can run HSPICE by typing the following command at the UNIX prompt,

```

grid hspice inputfile

```

where *inputfile* is the name of your netlist (default name is hspiceFinal). The output will be displayed on the screen. You can also store the output of HSPICE in an output file, as follows,

grid hspice inputfile > outputfile

the output file will be a text file and you can use any text editor to view it. It may be useful to check the output file when your HSPICE simulation is not successful.

**NOTE :** The following table lists the basic statements and elements of an HSPICE input file.

| Statement or element       | Definition                                                 |

|----------------------------|------------------------------------------------------------|

| title                      | first line is the input file title (considered as comment) |

| * or \$                    | designates comments to describe the circuit                |

| .OPTIONS                   | sets conditions for simulation                             |

| .DC/ .AC/ .TRAN            | analysis statement                                         |

| .PRINT/.PLOT/.GRAPH/.PROBE | statements to set print, plot and graph variables          |

| .IC/.NODESET               | set initial state; can also be put in subcircuits          |

| source (I or V)            | set input stimuli                                          |

| netlist                    | circuit description                                        |

| .LIB                       | library                                                    |

| .INCLUDE                   | general include files                                      |

| .MODEL                     | model description                                          |

| .PARAM                     | parameter definition                                       |

| .ALTER                     | sequence for in-line case analysis                         |

| .END                       | required statement to terminate the simulation             |

| .MEASURE                   | calculate time, power and etc.                             |

### 4.4 HSPICE Netlist Example

Here is an example that shows how a HSPICE netlist would look like. Try to understand each statement. *.measure*, *.param*, *.alter* are especially important because it would be very useful in later simulation of your own circuit.

```

* INVERTER

*_____

* Include model/library file

*_____

.lib "$CDK_DIR/models/hspice/public/publicModel/tsmc25N" NMOS

.lib "$CDK DIR/models/hspice/public/publicModel/tsmc25P" PMOS

*_____

* Parameters

* Several parameters are declared

* These parameters are used later in this file

*

_____

.param wn=300n

.param wp=700n

.param l=240n

.param vref=1.25

*_____

* NETLIST

* The width and length of the tr's are not

* numbers but the parameters

*_____

C0 OUT 0 20E-15 M=1.0

MP1 OUT IN VDD! VDD! TSMC25P L='l' W='wp'

+AD=+3.00000000E-13 AS=+3.0000000E-13 PD=+2.30000000E-06 PS=+2.3000000E-

06

+M=1

MN1 OUT IN 0 0 TSMC25N L='l' W='wn'

+AD=+3.00000000E-13 AS=+3.0000000E-13 PD=+2.30000000E-06 PS=+2.30000000E-

06

+M=1

*_____

* OPTIONS

*_____

.OPTIONS POST

.PRINT TRAN V(IN) V(OUT)

.TRAN 1.00000E-09 3.00000E-08 START= 0.

.TEMP 25.0000

*_____

* INPUT

*_____

.global vdd!

vvdd! vdd! 0 DC=2.5

vIN IN 0 pulse 0.0 2.5 1n 1n 1n 5n 10n

_____

* MEASURE

*_____

.measure tplh trig v(in) val=vref fall=1

+ targ v(out) val=vref rise=1

.measure a_power avg power from=0ns to=30ns

*_____

* ALTER

* HSPICE runs several times according to

* the number of .alter statement.

* In this example, HSPICE runs 5 times

* (1 for the initial value & 4 for the .alter's)

* The measurement results for each simulation

* will be stored in .mt0, .mt1, files.

*_____

```

```

.alter

.param wn=300n wp=700n

.alter

.param wn=300n wp=800n

.alter

.param wn=600n wp=900n

.alter

.param wn=600n wp=1200n

.end

```

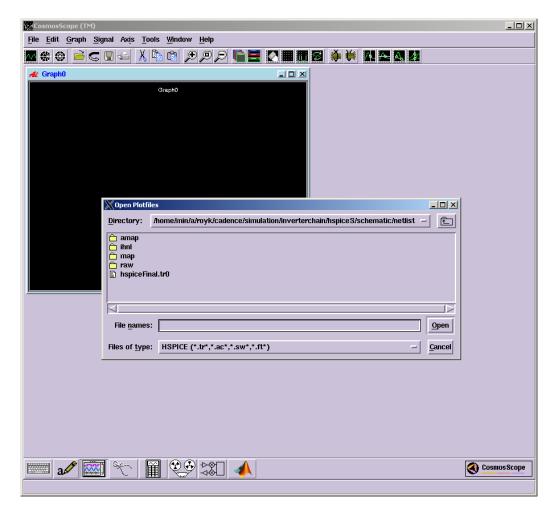

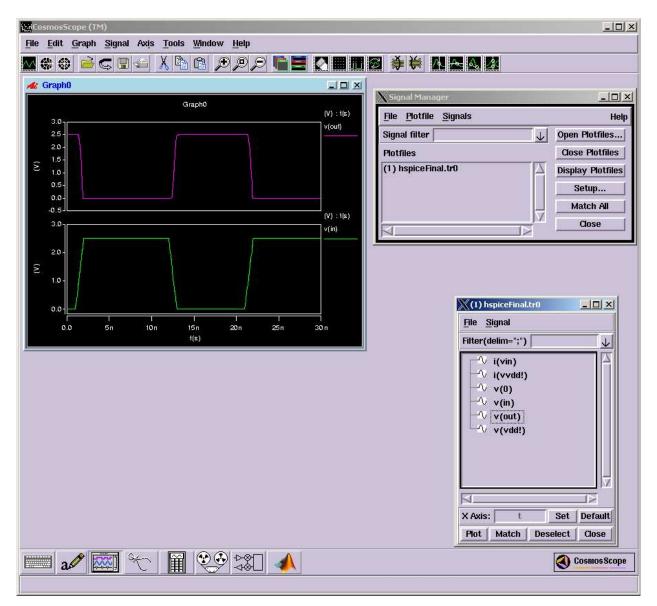

### 4.5 CosmosScope

*CosmosScope and Awaves* are graphical waveform viewer. In previous section, you ran HSPICE in command line and the simulation results can be seen by using either *CosmosScope* or *Awaves*. However *Awaves* is no longer supported on linux (ecegrid is a linux cluster). Hence we will not be using *Awaves* in this course.

• To run *CosmosScope*, enter grid scope in a terminal window command prompt. After the *CosmosScope* window is loaded, select **File -> Open -> Plotfiles** from the drop down menu.

• When the *Open Plotfiles* box appears, select *HSPICE(\*.tr\*,\*.ac\*,\*.sw\*,\*.ft\*)* in the *Files of type* drop box and enter the filename by typing or clicking the file in the browser window (hspiceFinal.tr0). Click **OPEN** when done. Two windows will appear - *Signal manager* and *Plot file window*. From Plot file window, select all the signal names and click PLOT. A new waveform window will appear showing the simulation results.

# 5 Nanosim

Nanosim is a transistor-level circuit simulator that can run simulations (with HSPICE-like accuracy) with a run time 10 to 1000 times faster than HSPICE. This would be very helpful especially when the design complexity increases as these simulations may take hours. This is the reason Nanosim comes under the category *Fast-SPICE*. There is another similar kind of tool from Synopsys that is *HSIM*.

Note that Nanosim is not set up to run under the *Analog Design Environment*. Therefore it is necessary to extract a netlist from your schematic under the *Analog Design Environment* and execute Nanosim from UNIX terminal command prompt. The stimuli and output set up in the *Analog Design Environment* will work in Nanosim, however, it might be easier and more efficient to use the Nanosim configuration file and input vector files to set up the inputs and outputs for designs.

### 5.1 Online Documentation

The online documentation for nanosim can be viewed by entering grid nssold at any UNIX command window. You will find there *nanosim user guide* as well as *nanosim command reference guide*.

#### 5.2 Netlist

Nanosim accepts several formats of netlists including HSPICE. The HSPICE netlist filename will need to have a .sp suffix for Nanosim to recognize it as an HSPICE netlist.

We will use the hspiceFinal file from *InverterTest* example. Since you need to modify the file hspiceFinal file a bit, copy the file to another file nanosim.sp.

cp hspiceFinal nanosim.sp

### 5.3 Configuration File

- The purpose of the configuration file is to add additional Nanosim commands to control the simulation. One of the more relevant uses is to specify the types of output that is to be reported or saved to a file (nanosim.out). Without specifying any output commands, no output will be reported or saved. Other uses include the option to perform power analysis of the circuit and to control the accuracy and speed of the simulation.

- To create a configuration file, use any text editor to create a text file with any name. The commands are line oriented and can be continued on the next line with the use of a space and a back slash (\) at the end of a line. Comments are preceded by a semicolon (;).

- The contents of the configuration file will depend on the type of simulation and types of results that one would like to obtain. A typical configuration file would contain the

following commands. Create a file with those commands in it and save the file as *nanosim.cfg*.

print\_node\_v IN\* OUT\_0 OUT\_1

print\_node\_logic IN\* OUT\_0 OUT\_1

report\_block\_powr total track\_power=1 \*

Node names can be replaced by the wildkey '\*' to specify that all nodes are to be printed or reported, however, this will cause lots of data to be generated unnecessarily.

The **print\_node\_v** command prints the voltage waveform information for the given nodes to the *.out* file.

The **print\_node\_logic** command tracks the logic values of the specified nodes and records their changes in the *.out* file.

The **report\_block\_powr** command creates a summary report of the power consumption of a specified circuit block.

The set\_sim\_eou [sim=1/2/3/4/5/6/7] [model=1/2/3/3.5/4/5/6/7] [net=1/2/3/4/5/6/7] controls the speed and accuracy of the simulation. Lower settings correspond to less accuracy-more performance and higher settings correspond to more accuracy-less performance. sim\_sim\_eou  $sim=2 \mod l=2 net=2$  is equivalent to a default NanoSim simulation. Please refer to the online documentation for more details of the above commands.

### 5.4 Running Nanosim

- To run Nanosim, the command is nanosim.

- The Nanosim command line used for this tutorial would be:

grid nanosim -n nanosim.sp -c nanosim.cfg -out fsdb -z tt

The -n command line option is the only required option to specify a netlist file.

The -c option is used to specify a configuration file. See the next section for further details on how to create the configuration file.

The -out option is used to specify the output file format. Later, you can see the simulation waveform by opening *nanosim.fsdb* file.

The -z option is to tell Nanosim to create technology files automatically which start with the name (tt) given. The reason for the name tt used is because it corresponds to the name of the *typical* process corner selected in the library files used. For the subsequent simulations, the -z option can be replaced by a -p option to save time and to re-use the technology files generated by -z. You will find two files created tt\_tech\_tsmc25p. The corresponding part of the

command using -p option would be -ptt\_tech\_tsmc25n tt\_tech\_tsmc25p. Note that you can remove the mention of library files from nanosim.sp.

### 5.5 Using Input Vector File

This example shows how to use a vector file in your simulation. Create a file named nanosim.vec as below.

| type nsvt<br>signal IN_0 IN_1          |

|----------------------------------------|

| period 20<br>fall 1<br>rise 1          |

| radix 1 1                              |

| 0 0<br>0 1<br>1 0<br>0 1<br>1 0<br>1 1 |

- The type nsvt command provides a method for reading in a file containing input stimuli and expected data values to be applied at fixed intervals. There are other types are well like type vec that provides a method for reading in a file containing input stimuli and expected data values that are organized in a tabular format, i.e., you can specify the time at which some input vector is applied.

- signal specifies the list of input/output signal names.

- period specifies the fixed time interval applied between two consecutive vectors in the nsvt file.

- fall and rise specify the *rise* and *fall* times in nanoseconds, respectively.

- radix specify the number of bits (the radix) associated with each input signal.

### 5.5.1 SPICE Netlist

The SPICE netlist file should look like as below. It was extracted from InverterTest design schematic. The input stimulus inside the netlist file should be removed or commented while doing nanosim simulation with vector file.

```

.GLOBAL VDD!

C2 OUT 0 0

10E-15 M=1.0

C1 OUT 1 0

10E-15 M=1.0

XI1 IN 0 INTERNAL 0 INVERTERP 1

XI2 INTERNAL_0 OUT_0 INVERTERP_1

XI3 IN_1 NET38 INVERTERP_1

XI4 NET38 INTERNAL_1 INVERTERP_1

XI5 INTERNAL 1 OUT 1 INVERTERP 1

.SUBCKT INVERTERP_1 IN OUT

MPO OUT IN VDD! VDD! TSMC25P L=(3E-07) W=(9E-07)

AD=+6.75000000E-13 +AS=+6.75000000E-13 PD=+3.3000000E-06

PS=+3.3000000E-06 M=1

MNO OUT IN 0 0 TSMC25N

L=(3E-07) W=(4.5E-07)

AD=+3.37500000E-13 +AS=+3.37500000E-13 PD=+2.40000000E-06

PS=+2.4000000E-06 M=1

.ENDS INVERTERP 1

.lib "$CDK DIR/models/hspice/public/publicModel/tsmc25N" NMOS

.lib "$CDK_DIR/models/hspice/public/publicModel/tsmc25P" PMOS

*.TRAN

1.00000E-09 5.00000E-08 START= 0.0000

.TEMP

25,0000

*.OP

*.save

*.OPTIONS POST

*vIN_1 IN_1 0 pulse 0 2.5v 1n 1n 1n 10n 20n

*vIN_0 IN_0 0 pulse 0 2.5v 1n 1n 1n 10n 20n

vvdd! vdd! 0 DC=2.5v

.END

```

#### 5.5.2 Command

grid nanosim -n nanosim.sp -c nanosim.cfg -nvec nanosim.vec -out fsdb -z tt

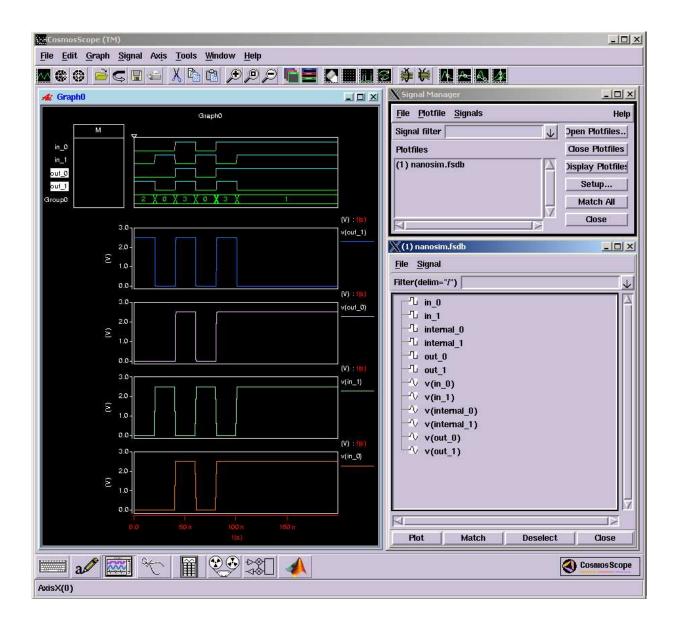

#### 5.6 CosmosScope

- *CosmosScope* is used to view the waveform results of a Nanosim simulation. It can display both digital and analog signals from the simulation.

- To run *CosmosScope*, enter grid scope in a terminal window command prompt. After the *CosmosScope* window is loaded, select **File** -> **Open** -> **Plotfiles** from the drop down menu. Select *FSDB* for *Files of type* and enter the filename by typing or clicking the file in the browser window (nanosim.fsdb). Click **OPEN** when done. Two windows will appear - *Signal manager* and *Plot file window*. From *Plot file window*, select all the signal names and click PLOT. A new waveform window will appear showing the simulation results.

• It is also possible to display signals as a bus. In the waveform window, select out\_0 and out\_1 (these are logic values) by clicking the names and click *create bus* icon. Note that only signals that are logic values can be displayed as buses.

• You can change the signal attributes by double-clicking the signal names.

## 5.7 Delay Measurement

Create a new configuration file with the following content.

```

print_meas_cmt

print_meas_path

meas_n2n_delay IN_0 - OUT_0 -

meas_n2n_delay IN_1 - OUT_1 -

```

The **print\_meas\_cmt** command prints BDC (Block Delay Calculation) commands to the SDF (Standard Delay Format) file. The name of the corresponding file would be nanosim.sdf.

The **print\_meas\_path** command prints paths found by BDC. The name of the corresponding file would be nanosim.path.

The **meas\_n2n\_delay** command measures node-to-node delay. The syntax is as follows.

```

meas_n2n_delay [print_neg=0|1] <source_node_name(s)> <edge>

<sink_node_name> <edge>

```

```

<edge> ::= (rise | fall | -) ['-' denotes both rise and fall]

```

### 5.7.1 Command

```

grid nanosim -n nanosim.sp -c nanosim.cfg -nvec nanosim.vec -out out -z tt

```

### 5.7.2 Running Simulation

You will get the following warning messages after running the above command.

nanosim: WARNING: BDC : No path found between rising edge of in\_0 and falling edge of out\_0 nanosim: WARNING: BDC : No path found between falling edge of in\_0 and rising edge of out\_0 nanosim: WARNING: BDC : No path found between rising edge of in\_1 and rising edge of out\_1 nanosim: WARNING: BDC : No path found between falling edge of in\_1 and falling edge of out\_1

Explain why these warning messages are coming.

#### 5.7.3 Viewing SDF and PATH Files

• In the generated *nanosim.sdf* file, you will find the following lines.

```

(IOPATH in_0 out_0 (0.220:0.220:0.220) (0.280:0.280:0.280))

(IOPATH in_1 out_1 (0.350:0.350:0.350) (0.260:0.260:0.260))

```

The two triples following are for the *rising* and *falling* delays, respectively. The first number in each triple is the *minimum delay*, the middle number is the *nominal delay*, and the third number is the *maximum delay*. The delays measured by NanoSim use only the minimum and maximum numbers. We have all the nominal, minimum, and maximum delays same as we are using only one typical technology library.

• View the *nanosim.path* file as well. It will tell you the complete signal propagation paths. *Example:* Path from in\_1 to out\_1 :

Node in\_1 is rising at time 20.500ns Node net38 is falling at time 20.590ns Node internal\_1 is rising at time 20.680ns Node out\_1 is falling at time 20.760ns

# 5.8 Using Graphical User Interface

Type grid nanosimgui from a command prompt. It should open the nanosim GUI where you can create a project work file.

• You can include a SPICE file at **Netlist & Stimulas → Pre-Layout** tab.

|               | bench (/home/min/<br>ion <u>V</u> iew <u>T</u> ools <u>A</u> r |                         |                                    |                                            | _101                |

|---------------|----------------------------------------------------------------|-------------------------|------------------------------------|--------------------------------------------|---------------------|

|               |                                                                |                         | teip                               |                                            |                     |

|               |                                                                | - A A                   | 888 UNIL 0                         |                                            |                     |

|               | <u>1</u> Netlist & Stime                                       | ulus                    | 2. Simulation Setup                | <u>3</u> . Simulation                      | <u>4</u> . Analysis |

| Dee 1         | a <u>v</u> out <u>P</u> ost-Layout                             | Verilog <u>G</u> ate Le | vel   <u>B</u> ehavioral Modelling | Netlist Options Vector Stimulus Save & I   |                     |

|               | ,                                                              | 0.85                    | ver   <u>b</u> enavioral Modelling | Neursi Options   Vector Summits   Save & I | Restore             |

| Pre-l         | ayout SPICE netlist file                                       | 5.                      |                                    |                                            |                     |

|               | SPICE Netlist<br>File Type                                     | * SPICE Netlist         | File                               |                                            |                     |

| 1             | HSPICE                                                         | /home/min/a/roy         | k/cadence/simulation/InverterTe    | st/hspiceS/schematic/netlist/nanosim.sp    |                     |

| 2             | _                                                              |                         |                                    |                                            |                     |

| 3             | -                                                              |                         |                                    |                                            |                     |

| 4             |                                                                | -                       |                                    |                                            |                     |

| a —           | _                                                              | -                       |                                    |                                            |                     |

| 6             | -                                                              |                         |                                    |                                            |                     |

| 8             |                                                                | -                       |                                    |                                            |                     |

| 9             | -                                                              |                         |                                    |                                            |                     |

| 10            |                                                                |                         |                                    |                                            |                     |

| 11            |                                                                |                         |                                    |                                            |                     |

| 12            |                                                                |                         |                                    |                                            |                     |

|               |                                                                |                         |                                    |                                            |                     |

| re-l          | ayout SPICE subckt lib                                         | rary paths:             |                                    |                                            |                     |

|               | Wenter colored                                                 | and the second second   |                                    |                                            |                     |

|               | * SPICE Subckt Lit                                             | orary Path              |                                    |                                            |                     |

| 1<br>2        | -                                                              |                         |                                    |                                            |                     |

| 2             | -                                                              |                         |                                    |                                            |                     |

| _             |                                                                |                         |                                    |                                            |                     |

|               |                                                                |                         |                                    |                                            |                     |

| r <u>k</u> in | g directory:                                                   |                         |                                    |                                            |                     |

|               | Sec                                                            |                         |                                    |                                            |                     |

| y             |                                                                |                         |                                    |                                            | Netlist & Stimulus  |

• You can include a vector file at **Netlist & Stimulas**  $\rightarrow$  **Vector Stimulas** tab.

|        | sbench (/home/min/a/ro<br>ion <u>V</u> iew <u>T</u> ools <u>A</u> nalysi | rk/nanosim/nanosim.wrk)<br>s <u>W</u> indow <u>H</u> elp                                                                      |         |

|--------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------|

| 7      | 🗃 🖬  🗛                                                                   | A A Sta In 9                                                                                                                  |         |

|        | <u>1</u> Netlist & Stimulus                                              | 2, Simulation Setup 3, Simulation 4, Analysis                                                                                 |         |

| re-L   | .a <u>v</u> out <u>P</u> ost-Layout \                                    | erliog <u>G</u> ate Level <u>B</u> ehavioral Modelling Netlist <u>Options</u> Vector Stim <u>u</u> lus Sav <u>e</u> & Restore |         |

| ljgit  | al vector stimulus files(Nar                                             | oSim/HSPICE):                                                                                                                 |         |

|        | Vector Stimulus Netli<br>File Type                                       | at 👫 Vector Stimulus Netlist File                                                                                             |         |

| 1      | vec                                                                      | home/min/a/royk/cadence/simulation/inverterTest/hspiceS/schematic/netlist/nanosim.vec/                                        |         |

| 2      |                                                                          |                                                                                                                               |         |

| 3      |                                                                          |                                                                                                                               |         |

| 4      | -                                                                        |                                                                                                                               |         |

| 5      | -                                                                        |                                                                                                                               |         |

| 6      | -                                                                        |                                                                                                                               |         |

| 8      | -                                                                        |                                                                                                                               |         |

| 10     | -                                                                        |                                                                                                                               |         |

| eril   | og VCD stimulus:                                                         |                                                                                                                               |         |

|        | * Signal Name File                                                       | * VCD File                                                                                                                    |         |

| 1      |                                                                          |                                                                                                                               |         |

| 2      |                                                                          |                                                                                                                               |         |

| 3      |                                                                          |                                                                                                                               |         |

| 4      | -                                                                        |                                                                                                                               |         |

| 5<br>6 | -                                                                        |                                                                                                                               |         |

| 7      |                                                                          |                                                                                                                               |         |

| 8      |                                                                          |                                                                                                                               |         |

|        |                                                                          |                                                                                                                               |         |

| kin    | g directory:                                                             |                                                                                                                               |         |

|        |                                                                          | ( management                                                                                                                  |         |

| у      |                                                                          | Notist &                                                                                                                      | Stimulu |

• You can insert commands from **Simulation Setup** → **Manual Commands** tab. The commands will be automatically included in the nanosim configuration file for simulation.

| ) 😅 🖬 🗛 🗛                                                        | A* 😫 lille 😵                                                                                                    |                                                           |                                    |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|

| <u>1</u> . Netlist & Stimulus                                    | 2. Simulation Setup                                                                                             | 3. Simulation                                             | <u>4.</u> Analysis                 |

| curacy/Performance Tech <u>Fi</u> les                            | Behavi <u>o</u> ral Timing <u>D</u> iagnostics                                                                  | <u>Pwr Diagnostics</u> <u>M</u> anual Cmds Glo <u>b</u> a | Cmds Waveform O/P                  |

|                                                                  |                                                                                                                 | commands here manually is recommended                     | than editing the config file as it |

| Config Commands                                                  | report_block_powr top track_power=1<br>print_meas_cmt                                                           | 1 track_wasted=1 split_wasted=1 *                         |                                    |

| Block Delay Calculation (BD                                      | print_meas_path                                                                                                 |                                                           |                                    |

| add_model_port<br>build model bdc                                | meas_n2n_delay IN_0 - OUT_0 -<br>meas_n2n_delay IN_1 - OUT_1 -                                                  |                                                           |                                    |

| -define_n2n_cause                                                | The second se |                                                           |                                    |

| meas n2n_delay                                                   |                                                                                                                 |                                                           |                                    |

| meas_n2n_hold                                                    |                                                                                                                 |                                                           |                                    |

| meas_n2n_setup                                                   |                                                                                                                 |                                                           |                                    |

| meas_node_cap                                                    |                                                                                                                 |                                                           |                                    |

| meas_pulse_width                                                 |                                                                                                                 |                                                           |                                    |

| print_meas_cmt<br>print_meas_path                                | -1                                                                                                              |                                                           |                                    |

| Command Name: meas n2n delay                                     |                                                                                                                 |                                                           | - 192                              |

| command warne, meas_nzh_delay                                    |                                                                                                                 |                                                           | -                                  |

| Syntax:                                                          |                                                                                                                 |                                                           |                                    |

| <pre><sink name="" node=""> <edge></edge></sink></pre>           | <source_node_name(s)> <edge></edge></source_node_name(s)>                                                       |                                                           | _                                  |