## EE559: MOS VLSI Design

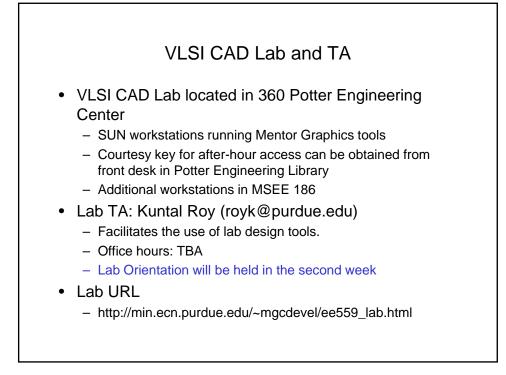

Instructors: K. Roy Email: kaushik@ecn.purdue.edu URL1: <u>www.ece.purdue.edu/~kaushik</u> Office: MSEE 232 Telephone: 494-2361 Office Hours: Tuesday/Thursday 11am-12noon or by appointments

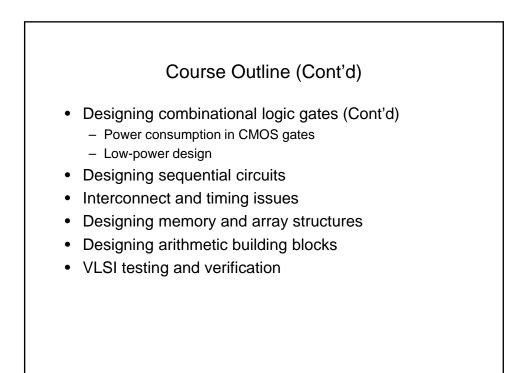

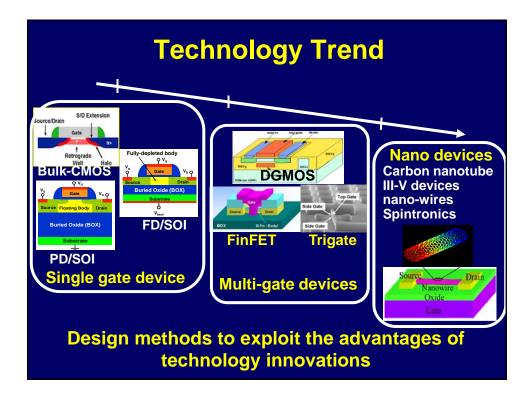

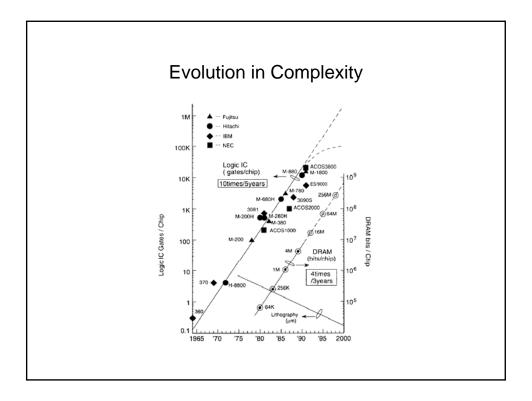

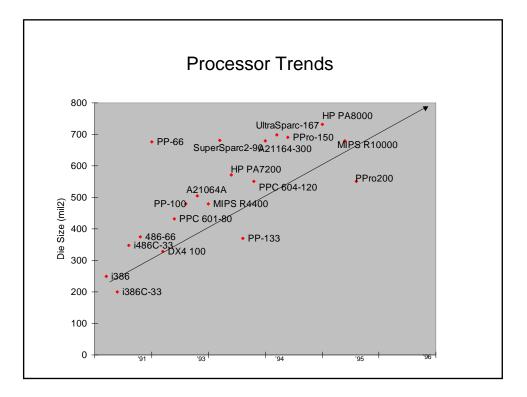

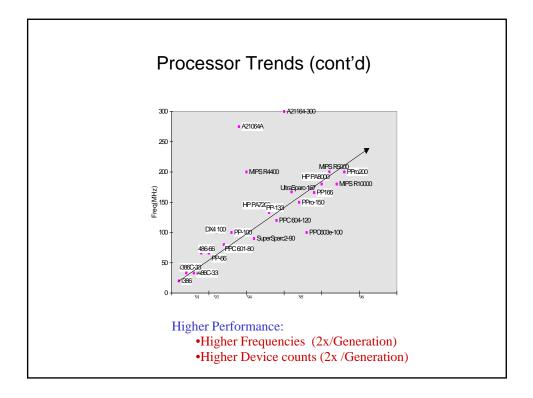

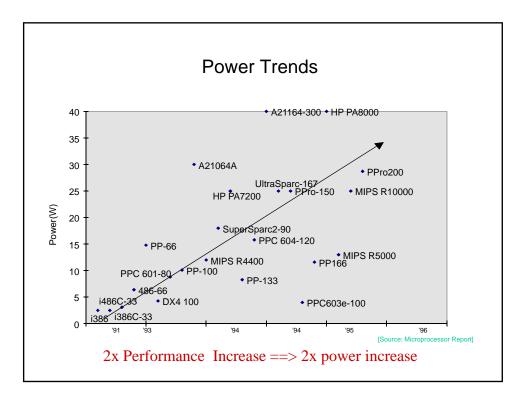

- Introduction: Historical perspective and Future Trend

- Semiconductor Devices

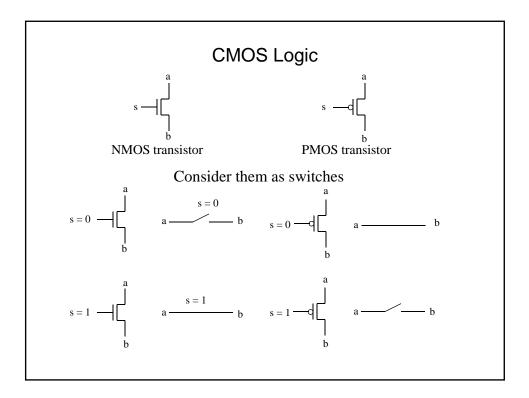

- CMOS Logic, Layout techniques

- MOS devices, SPICE models

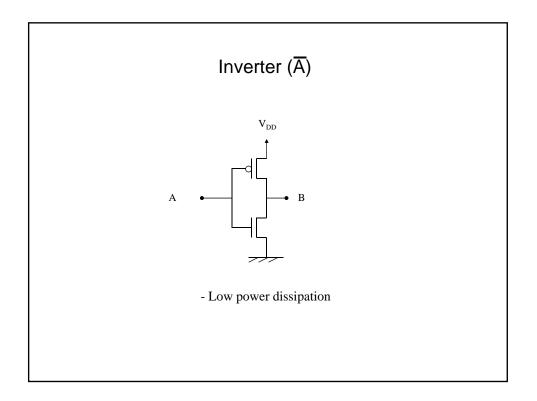

- Inverters: transfer characteristics, static and dynamic behavior, power and energy consumption of static MOS inverters

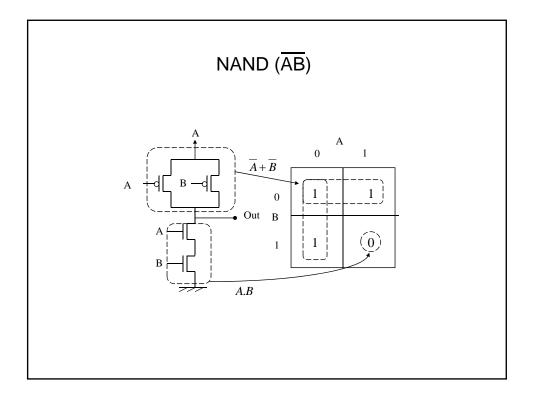

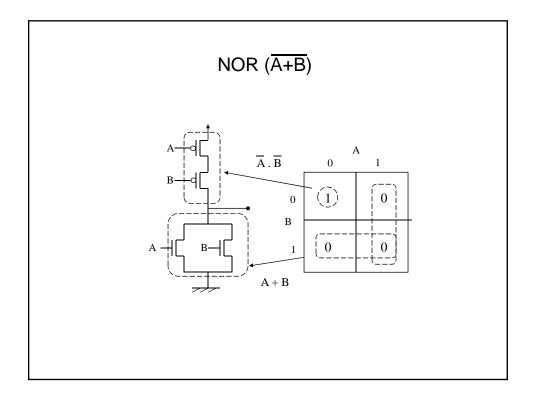

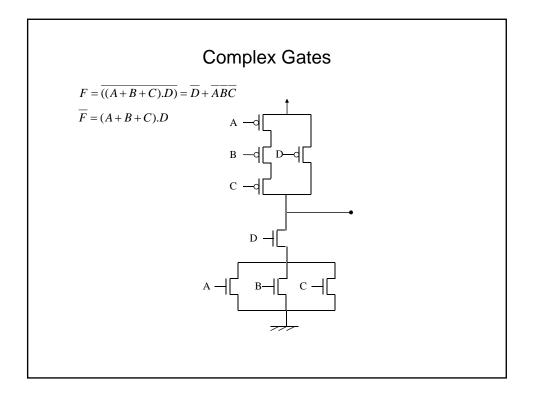

- Designing combinational logic gates in CMOS

- Static CMOS design: Complementary CMOS, ratioed logic, pass-transistor logic

- Dynamic CMOS logic

## HISTORY

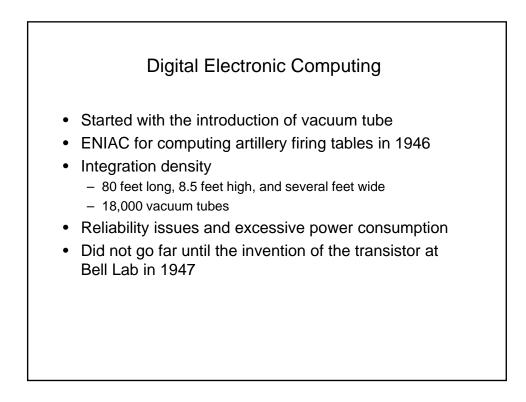

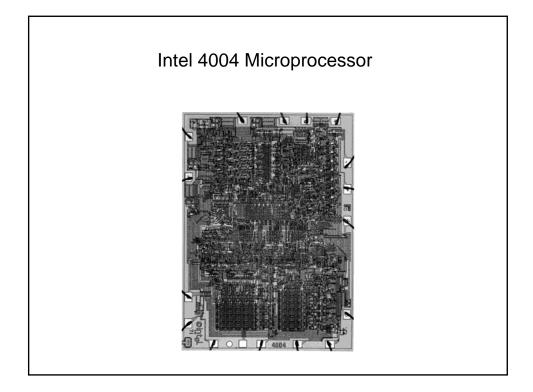

- MOS field-effect transistor: Lilienfeld (1925), Heil (1935)

- Bipolar transistors: Bardeen (1947), Schockley (1949)

- First Bipolar digital logic: Harris (1956)

- IC Logic family:

- Transistor-Transistor Logic (TTL) (1962)

- Emitter-Coupled Logic (ECL) (1971)

- Integrated Injection Logic (I<sup>2</sup>L) (1972)

- PMOS and NMOS transistors on the same substrate: Weimer (1962), Wanlass (1965)

- PMOS-only logic until 1971 when NMOS technology emerged

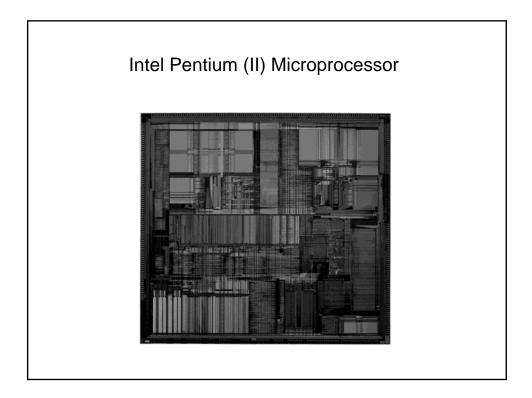

- NMOS-only logic until late 1970s, when CMOS technology took over

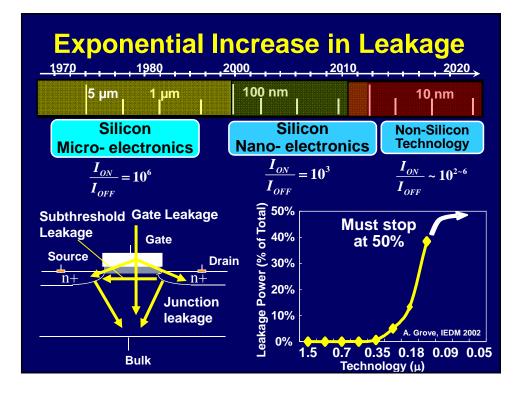

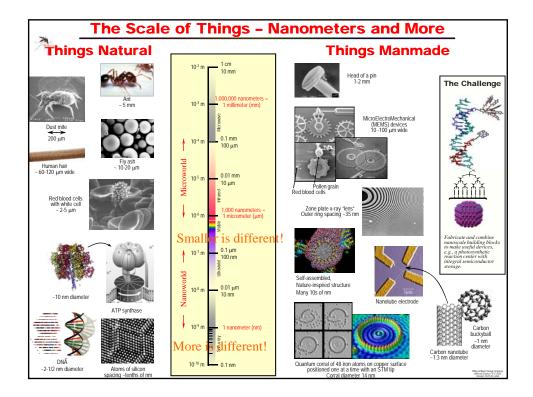

- Later developments: BiCMOS, GaAs, low-temperator CMOS, super-conducting technologies, Nano-electronic

| Heat Dissipa | ation |

|--------------|-------|

|--------------|-------|

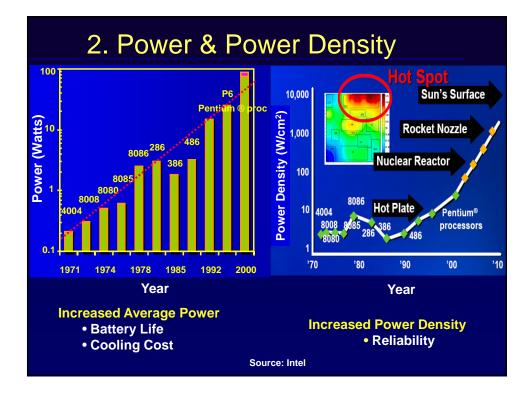

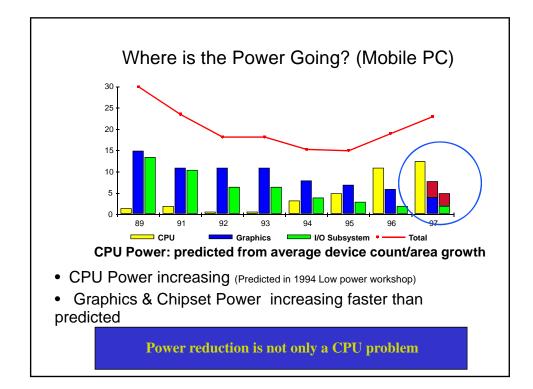

- Chips fail when they get hot

- · Need compact and cost-effective cooling solns

| <u>CPU</u>    | Thermal Soln Cost                           |

|---------------|---------------------------------------------|

| 486/33mhz     | HeatSink \$0.50                             |

| 486DX2 66mhz  | Heatsink \$1.00                             |

| Pentium 66mhz | Larger Heatsink \$2.00<br>System Fan \$4.00 |

- Cooling Solns will become more exotic/expensive

Extruded Heatsinks, Heatpipes, Blowers, Noise....

- Every Watt impacts System Cost, esp. for HVM

| Year     1998     2001     2004     2007     2010       # transistors     28M     64M     150M     350M     800M       On-Chip Clock (MHz)     450     600     800     1000     1100       Area (mm²)     300     360     430     520     620 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-Chip Clock (MHz)     450     600     800     1000     1100       Area (mm²)     300     360     430     520     620                                                                                                                        |

| Area (mm²)     300     360     430     520     620                                                                                                                                                                                            |

|                                                                                                                                                                                                                                               |

| Wiring Levels     5     5-6     6     6-7     7-8                                                                                                                                                                                             |

| Wiring Levels     5     5-6     6     6-7     7-8                                                                                                                                                                                             |

1

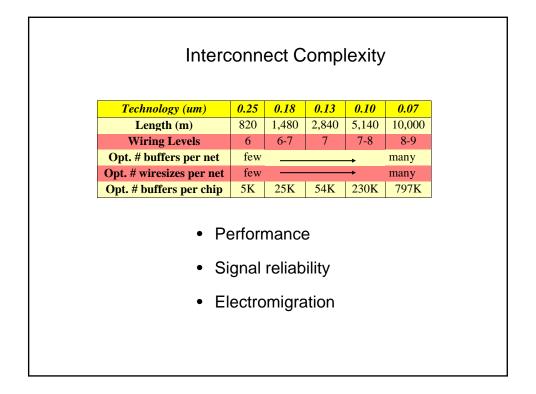

| Technology (um)           | 0.25  | 0.18  | 0.15  | 0.13  | 0.10  | 0.07  |

|---------------------------|-------|-------|-------|-------|-------|-------|

| 2cm line delay (ns)       | 2.589 | 2.480 | 2.650 | 2.620 | 3.730 | 4.670 |

| 1mm line delay (ns)       | 0.059 | 0.049 | 0.051 | 0.044 | 0.052 | 0.042 |

| Intrinsic gate delay (ns) | 0.071 | 0.051 | 0.049 | 0.045 | 0.039 | 0.022 |

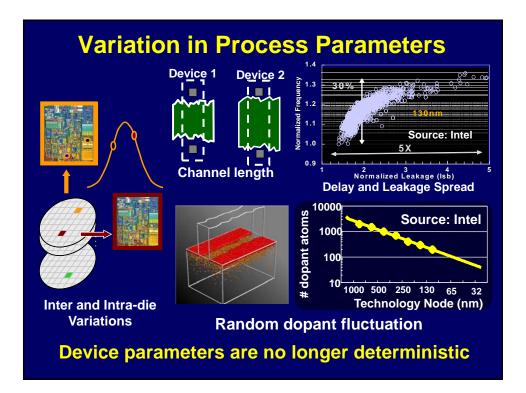

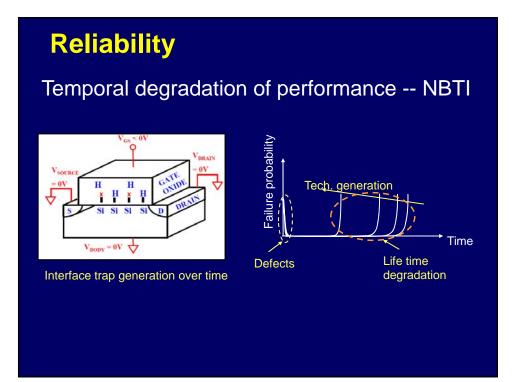

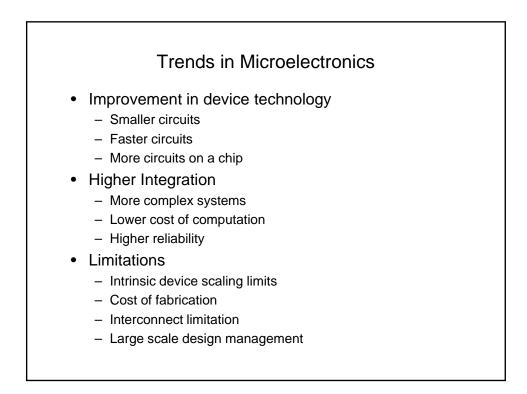

## **Problems of Microelectronics**

- Design Cost:

- design time

- fabrication time

- impossibility to repair

- reduce design cost to be competitive in price

- Marketing Issues:

- use most recent technologies to stay competitive in performance

- volume production is inexpensive

- time-to-market is critical

- evolving market

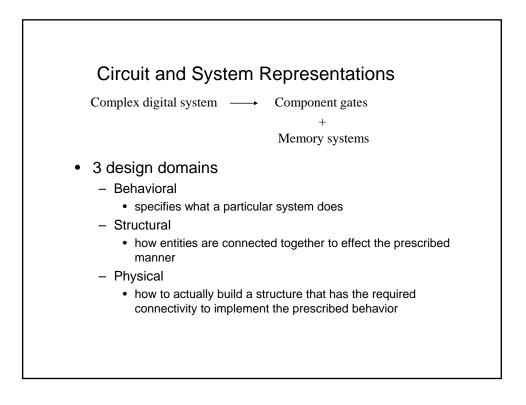

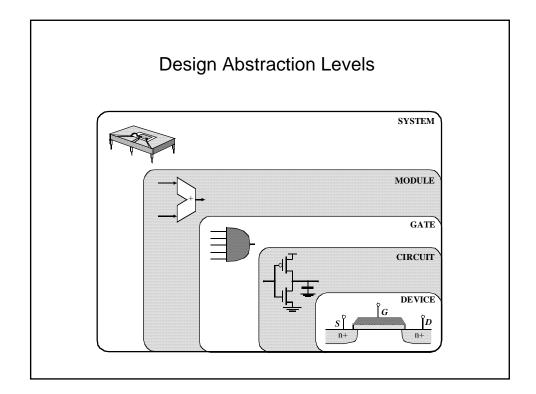

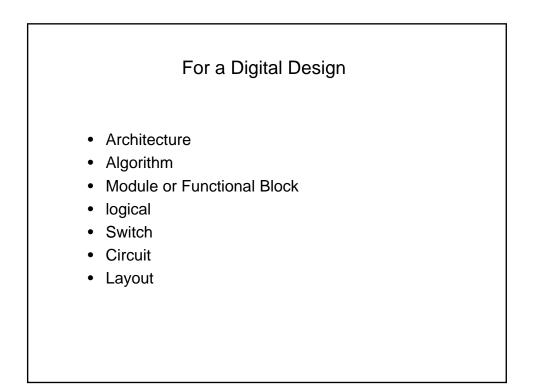

- Solution:

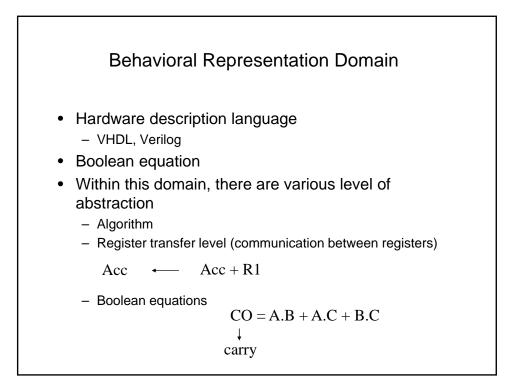

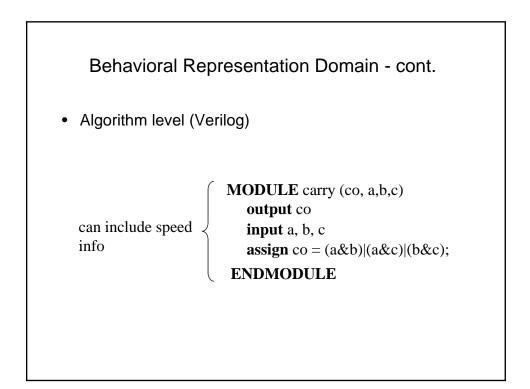

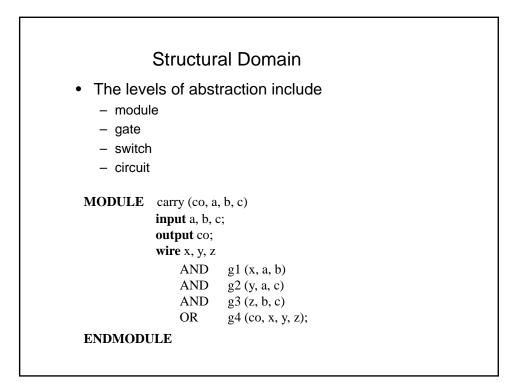

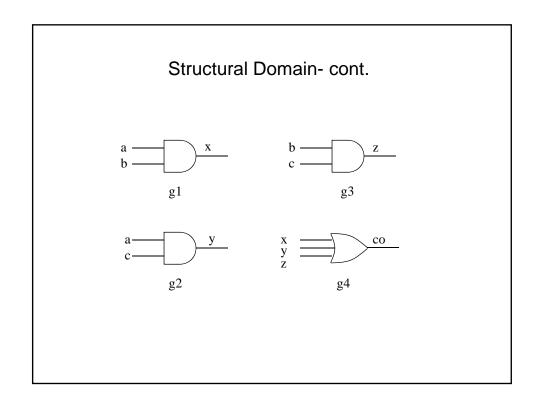

- Hierarchical and abstraction

- Different design styles

- Computer-Aided-Design

| Transistor Level                            |                                   |  |  |  |  |

|---------------------------------------------|-----------------------------------|--|--|--|--|

| <b>MODULE</b> carry (co, a, b, c)           |                                   |  |  |  |  |

| input a, b, c;                              |                                   |  |  |  |  |

| <b>output</b> co;<br><b>wire</b> i1, i2, i3 | 3. i4. cn:                        |  |  |  |  |

| NMOS                                        | n1(i1, vss, a)<br>n2(i1, vss, b)  |  |  |  |  |

|                                             |                                   |  |  |  |  |

|                                             | p1(i3, vdd, b);<br>p2(cn, i3, a); |  |  |  |  |

| ENDMODULE                                   |                                   |  |  |  |  |

|                                             |                                   |  |  |  |  |

|         | Physical Representation                                                                                                                                                                     |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODULE  | carry ;<br>Input a, b, c;<br>output co;<br>boundary [0, 0, 100, 400]<br>port a aluminum width = 1 origin = [0,2]<br>port b aluminum width = 1 origin = [0,7]<br>port<br>Port ci polysilicon |

| ENDMODU | LE                                                                                                                                                                                          |

|         |                                                                                                                                                                                             |