#### Digital Integrated Circuits A Design Perspective

Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic

## The Wire

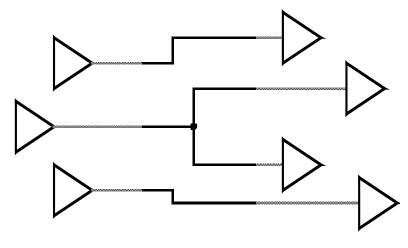

#### The Wire

transm itters

receivers

#### schematics

physical

## Interconnect Impact on Chip

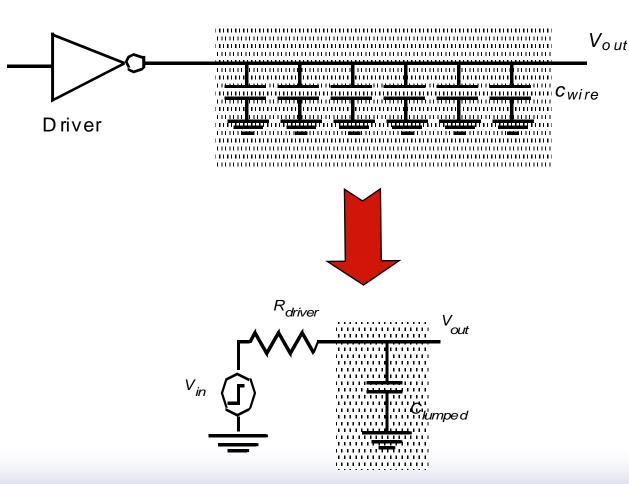

#### Wire Models

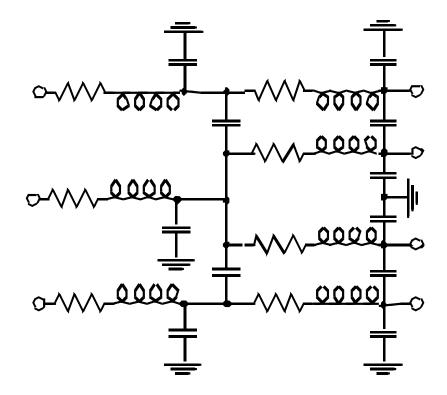

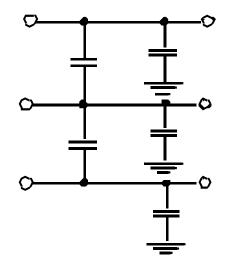

All-inclusive model

Capacitance-only

### Impact of Interconnect Parasitics

Interconnect parasitics

- reduce reliability

- affect performance and power consumption

#### Classes of parasitics

- Capacitive

- Resistive

- Inductive

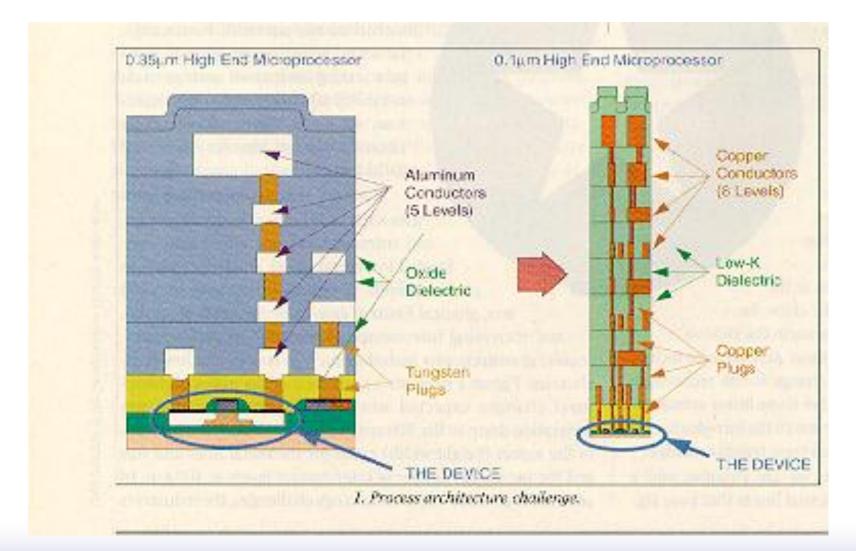

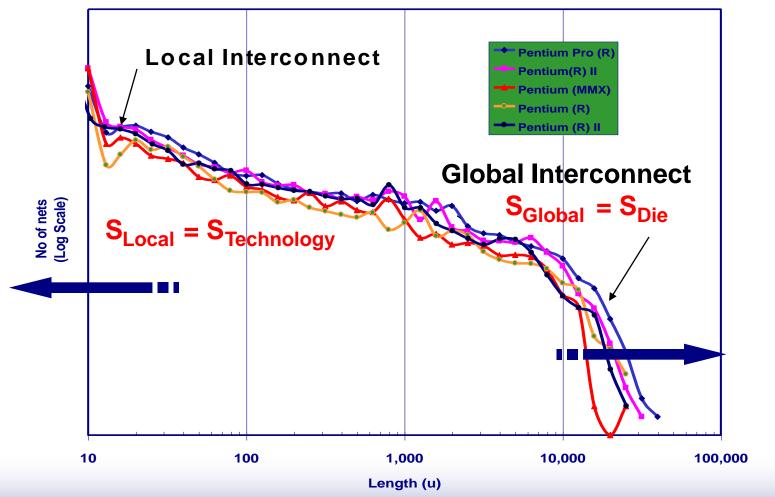

#### Nature of Interconnect

Source: Intel

Wires<sup>6</sup>

#### INTERCONNECT

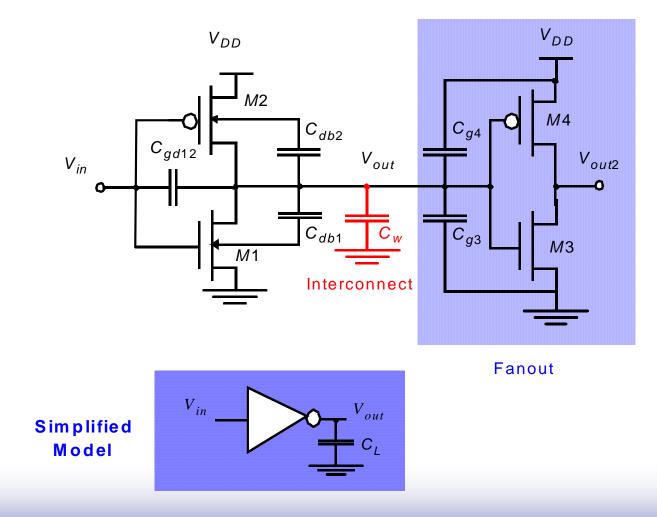

#### **Capacitance of Wire Interconnect**

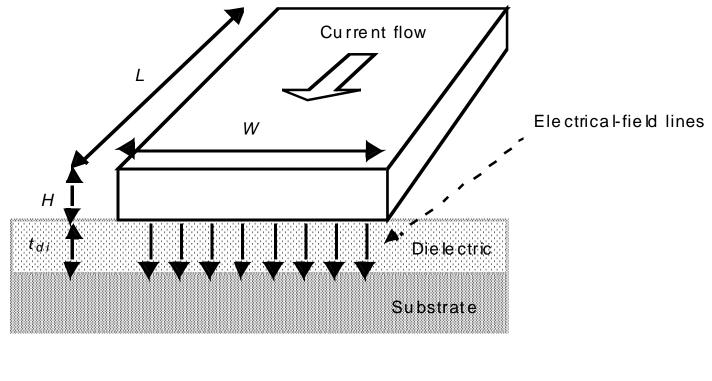

#### **Capacitance: The Parallel Plate Model**

$S_{Cwire} = \frac{S}{S \cdot S_L} = \frac{1}{S_L}$

$$c_{int} = \frac{\mathcal{E}_{di}}{t_{di}} WL$$

© Digital Integrated Circuits<sup>2nd</sup>

9 Wires

| Material                                          | ε <sub>r</sub> |

|---------------------------------------------------|----------------|

| Free space                                        | 1              |

| Aerogels                                          | ~1.5           |

| Polyimides (organic)                              | 3-4            |

| Silicon dioxide                                   | 3.9            |

| Glass-epoxy (PC board)                            | 5              |

| Silicon Nitride (Si <sub>3</sub> N <sub>4</sub> ) | 7.5            |

| Alumina (package)                                 | 9.5            |

| Silicon                                           | 11.7           |

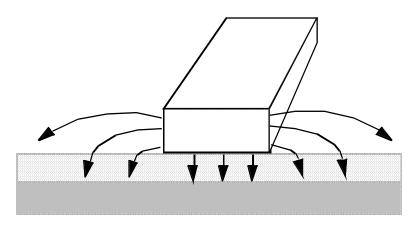

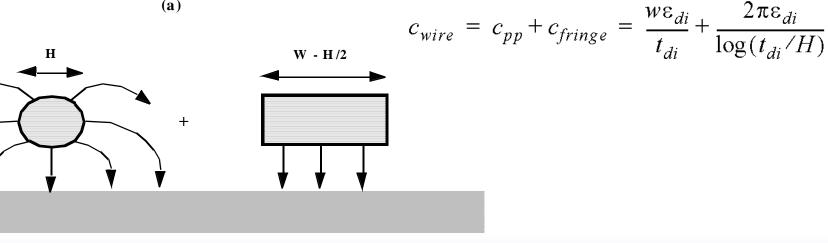

### **Fringing Capacitance**

**(a)**

**(b)**

© Digital Integrated Circuits<sup>2nd</sup>

11 Wires

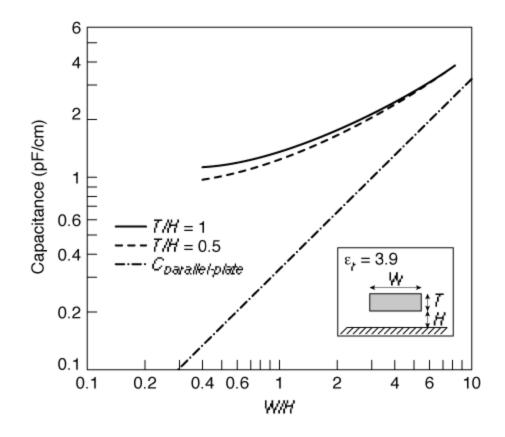

#### **Fringing versus Parallel Plate**

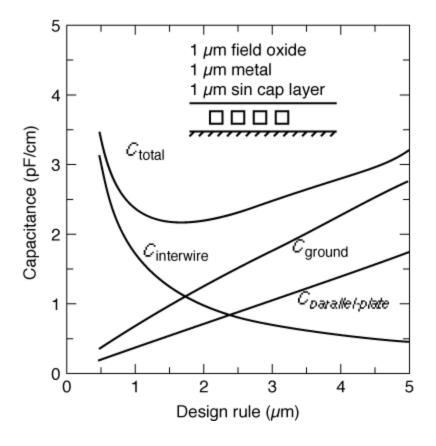

(from [Bakoglu89])

12 Wires

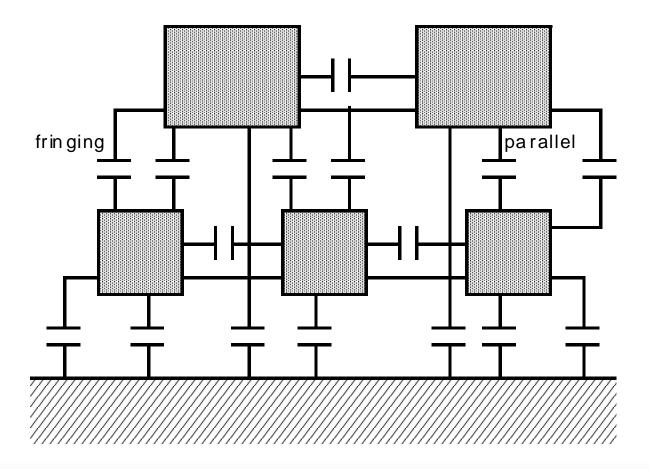

### Interwire Capacitance

13 Wires

#### **Impact of Interwire Capacitance**

(from [Bakoglu89])

## Wiring Capacitances (0.25 µm CMOS)

|      | Field | Active | Poly | Al1 | Al2 | Al3 | Al4 |

|------|-------|--------|------|-----|-----|-----|-----|

| Poly | 88    |        |      |     |     |     |     |

|      | 54    |        |      |     |     |     |     |

| Al1  | 30    | 41     | 57   |     |     |     |     |

|      | 40    | 47     | 54   |     |     |     |     |

| Al2  | 13    | 15     | 17   | 36  |     |     |     |

|      | 25    | 27     | 29   | -45 |     |     |     |

| Al3  | 8.9   | 9.4    | 10   | 15  | 41  |     |     |

|      | 18    | 19     | 20   | 27  | 49  |     |     |

| Al4  | 6.5   | 6.8    | 7    | 8.9 | 15  | 35  |     |

|      | 14    | 15     | 15   | 18  | 27  | 45  |     |

| Al5  | 5.2   | 5.4    | 5.4  | 6.6 | 9.1 | 14  | 38  |

|      | 12    | 12     | 12   | 14  | 19  | 27  | 52  |

#### INTERCONNECT

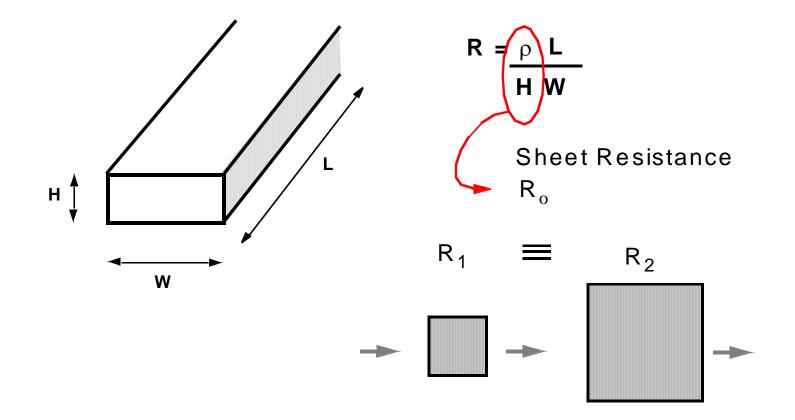

#### Wire Resistance

#### Interconnect Resistance

| Material      | ρ (Ω- <b>m</b> )     |

|---------------|----------------------|

| Silver (Ag)   | $1.6 \times 10^{-8}$ |

| Copper (Cu)   | $1.7 \times 10^{-8}$ |

| Gold (Au)     | $2.2 \times 10^{-8}$ |

| Aluminum (Al) | $2.7 \times 10^{-8}$ |

| Tungsten (W)  | $5.5 \times 10^{-8}$ |

#### **Dealing with Resistance**

## Selective Technology Scaling Use Better Interconnect Materials

- reduce average wire-length

- e.g. copper, silicides

#### More Interconnect Layers

reduce average wire-length

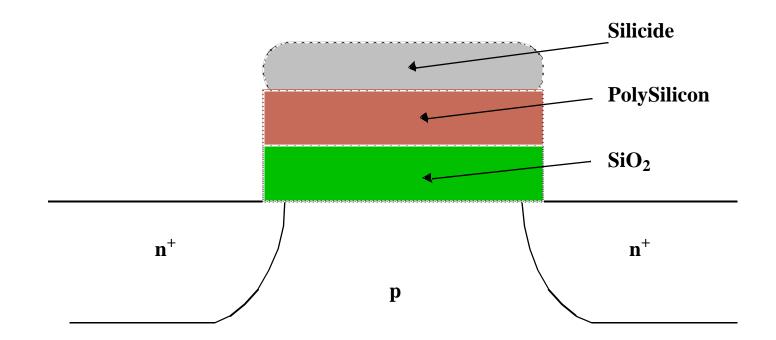

#### **Polycide Gate MOSFET**

Silicides: WSi 2, TiSi 2, PtSi 2 and TaSi

Conductivity: 8-10 times better than Poly

#### **Sheet Resistance**

| Material                                | Sheet Resistance ( $\Omega/\Box$ ) |  |

|-----------------------------------------|------------------------------------|--|

| n- or p-well diffusion                  | 1000 - 1500                        |  |

| $n^+, p^+$ diffusion                    | 50 - 150                           |  |

| $n^+$ , $p^+$ diffusion with silicide   | 3 - 5                              |  |

| $n^+$ , $p^+$ polysilicon               | 150 - 200                          |  |

| $n^+$ , $p^+$ polysilicon with silicide | 4 – 5                              |  |

| Aluminum                                | 0.05 - 0.1                         |  |

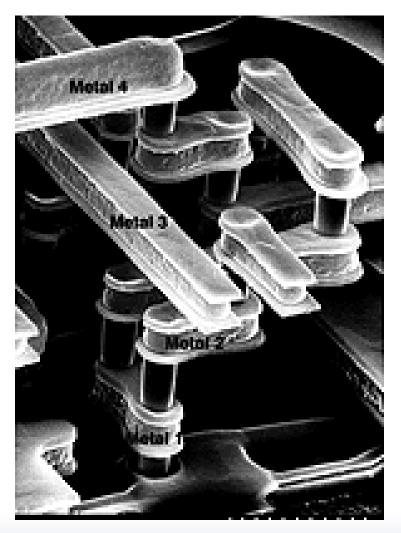

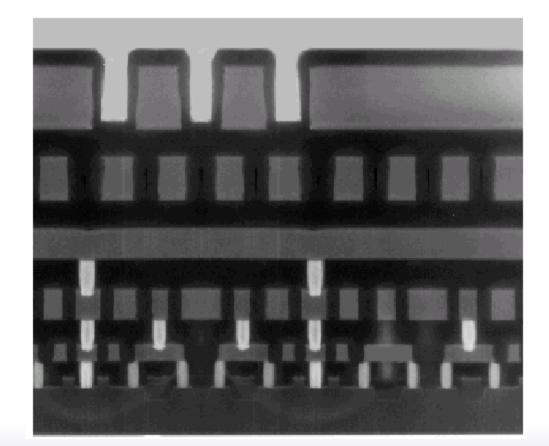

#### **Modern Interconnect**

#### **Example: Intel 0.25 micron Process**

#### 5 metal layers Ti/AI - Cu/Ti/TiN Polysilicon dielectric

| LAYER       | PITCH | THICK | A.R. |

|-------------|-------|-------|------|

| Isolation   | 0.67  | 0.40  | -    |

| Polysilicon | 0.64  | 0.25  | -    |

| Metal 1     | 0.64  | 0.48  | 1.5  |

| Metal 2     | 0.93  | 0.90  | 1.9  |

| Metal 3     | 0.93  | 0.90  | 1.9  |

| Metal 4     | 1.60  | 1.33  | 1.7  |

| Metal 5     | 2.56  | 1.90  | 1.5  |

|             | μm    | μm    |      |

Layer pitch, thickness and aspect ratio

#### INTERCONNECT

#### Interconnect Modeling

© Digital Integrated Circuits<sup>2nd</sup>

25 Wires

#### **The Lumped Model**

26 Wires

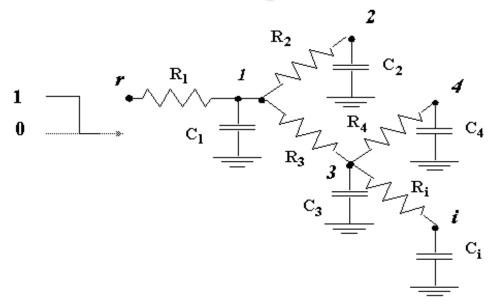

#### The Lumped RC-Model The Elmore Delay

$$R_{ik} = \sum R_j \Longrightarrow (R_j \in [path(s \to i) \cap path(s \to k)])$$

$$\tau_{Di} = \sum_{k=1}^{N} C_k R_{ik}$$

© Digital Integrated Circuits<sup>2nd</sup>

27 Wires

#### The Ellmore Delay RC Chain

$$\tau_N = \sum_{i=1}^{N} R_i \sum_{j=i}^{N} C_j = \sum_{i=1}^{N} C_i \sum_{j=1}^{R} R_j$$

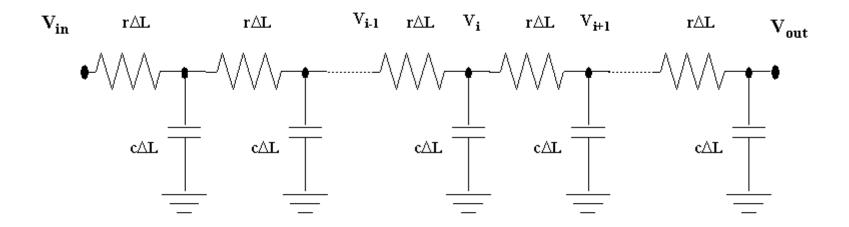

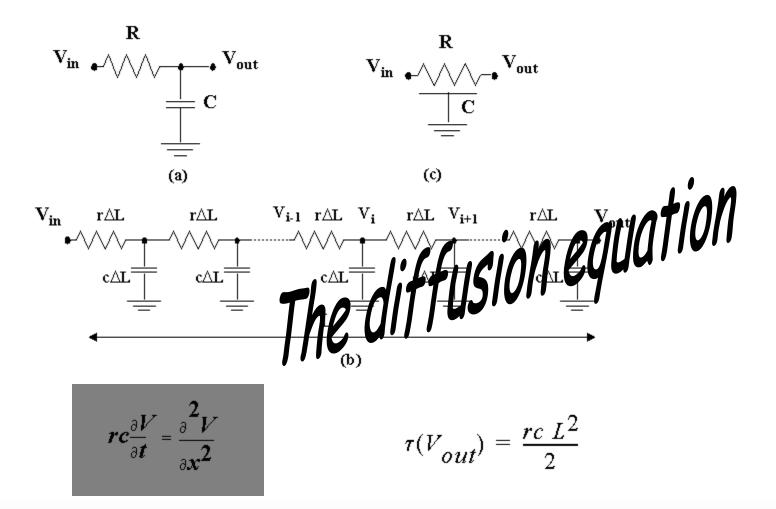

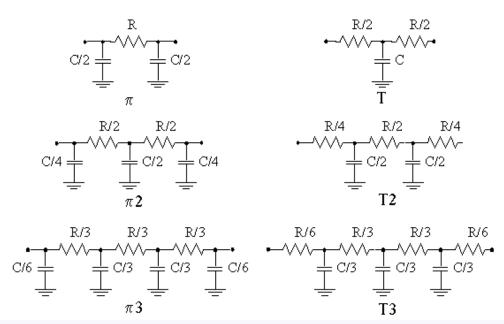

#### Wire Model

Assume: Wire modeled by N equal-length segments

$$\pi_{DN} = \left(\frac{L}{N}\right)^2 (rc + 2rc + \dots + Nrc) = (rcL^2) \frac{N(N+1)}{2N^2} = RC \frac{N+1}{2N}$$

For large values of N:

$$\tau_{DN} = \frac{RC}{2} = \frac{rcL^2}{2}$$

#### **The Distributed RC-line**

© Digital Integrated Circuits<sup>2nd</sup>

30 Wires

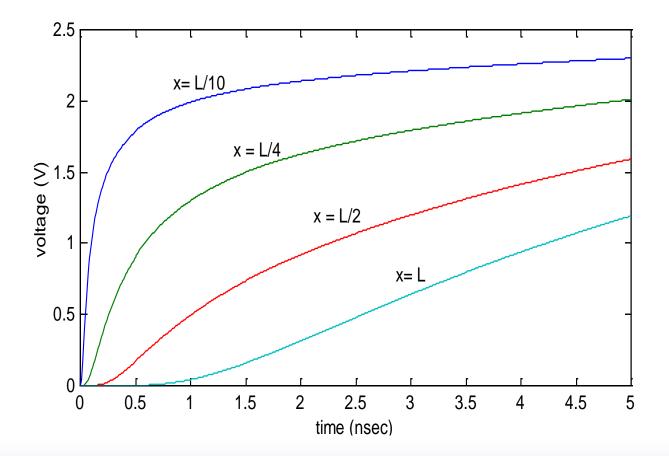

# Step-response of RC wire as a function of time and space

#### **RC-Models**

| Voltage Range                                         | Lumped RC-<br>network | Distributed<br>RC-network |

|-------------------------------------------------------|-----------------------|---------------------------|

| $0 {\rightarrow} 50\%$ (t <sub>p</sub> )              | 0.69 RC               | 0.38 RC                   |

| <b>0→63%</b> (7)                                      | RC                    | 0.5 RC                    |

| <b>10%</b> $\rightarrow$ <b>90%</b> (t <sub>r</sub> ) | 2.2 RC                | 0.9 RC                    |

Step Response of Lumped and Distributed RC Networks: Points of Interest.

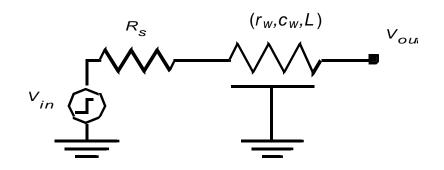

#### **Driving an RC-line**

$$\tau_D = R_s C_w + \frac{R_w C_w}{2} = R_s C_w + 0.5 r_w c_w L^2$$

$$t_p = 0.69R_s C_w + 0.38R_w C_w$$

© Digital Integrated Circuits<sup>2nd</sup>

33 Wires

#### **Design Rules of Thumb**

□ rc delays should only be considered when t<sub>pRC</sub> >> t<sub>pgate</sub> of the driving gate Lcrit >> √ t<sub>pgate</sub>/0.38rc

□ rc delays should only be considered when the rise (fall) time at the line input is smaller than RC, the rise (fall) time of the line

#### $t_{\rm rise} < {\rm RC}$

when not met, the change in the signal is slower than the propagation delay of the wire