## Metal-oxide-semiconductor field-effect transistors on GaAs (111)A surface with atomic-layer-deposited $Al_2O_3$ as gate dielectrics

M. Xu, Y. Q. Wu, O. Koybasi, T. Shen, and P. D. Ye<sup>a)</sup>

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue University,

West Lafayette, Indiana 47907, USA

(Received 3 April 2009; accepted 11 May 2009; published online 28 May 2009)

GaAs inversion-mode metal-oxide-semiconductor field-effect transistors (MOSFETs) with atomic-layer-deposited  $Al_2O_3$  as gate dielectrics are fabricated on (111)A and (100) surfaces. With the same channel length of 0.75  $\mu$ m, the maximum drain current of 15 mA/mm on n-channel MOSFET is obtained on (111)A surface, in great contrast to only 1  $\mu$ A/mm on (100) surface. For p-channel MOSFETs, maximum drain currents of 0.17 mA/mm and 0.8 mA/mm are obtained on (111)A and (100) surfaces, respectively. An empirical model is proposed to correlate the experimental observation with the existing III-V MOS theories. © 2009 American Institute of Physics. [DOI: 10.1063/1.3147218]

Silicon-based complementary metal-oxide-semiconductor (CMOS) devices with traditional structures are approaching fundamental physical limits. Researchers are looking for ways to continue the trend of scaling by using alternative materials such as Ge and III-V compound semiconductors that could out-perform Si-based CMOS. Recently, an increasing number of III-V metal-oxide-semiconductor fieldeffect transistor (MOSFET) papers were published with high indium concentration channels showing the promising onstate device performance. 1-8 Fermi-level unpinning and strong inversion is realized in In-rich InGaAs with different gate dielectrics. 9-11 However, GaAs MOSFETs with directly deposited high-k dielectrics remain a big challenge, most showing minuscule drain currents. 12-14 Encouraging results are obtained with silicon interfacial layer, in particular, with saline passivation. <sup>15–17</sup> GaAs is of great importance for scientific understanding of III-V interfaces and also practical applications due to its high electron mobility, high saturation velocity, and wide bandgap. GaAs MOS devices can be used as a sensitive test bed for all dielectric techniques. The passivation technique developed on GaAs can naturally be applied to InGaAs or other III-V semiconductors.

In this letter, we systematically study the electrical properties of inversion-mode *n*-channel MOSFETs (NMOSFETs) and *p*-channel MOSFETs (PMOSFETs) on both GaAs (111)A and (100) surfaces with atomic-layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> as gate dielectrics. (111)A is a pure Ga polar surface in contrast to (100) Ga–As nonpolar surface. The device work confirms that Fermi-level of GaAs (111)A surface is unpinned at the midgap with direct ALD Al<sub>2</sub>O<sub>3</sub>. The results obtained on GaAs (111)A surface are astonishingly different from those on GaAs (100) surface. An empirical model based on trap neutral level is proposed to correlate the experimental observation with the existing III-V MOS theories.

MOSFET fabrication starts with 2 in. semi-insulating GaAs (111)A or (100) substrates. After surface degreasing and ammonia-based native oxide etching, the wafers were transferred via room ambient to an ASM F-120 ALD reactor.

A 30 nm thick Al<sub>2</sub>O<sub>3</sub> layer was deposited at a substrate temperature of 300 °C as an encapsulation layer. Source and drain regions were selectively implanted with Si for NMOS-FETs and Zn for PMOSFETs with the same dose of 5  $\times 10^{14}$  cm<sup>-2</sup> at 40 keV through the 30 nm thick Al<sub>2</sub>O<sub>3</sub> layer. Implantation activation was achieved by rapid thermal anneal (RTA) at 820 °C for 15 s in nitrogen ambient for NMOSFETs and at 750 °C for 15 s for PMOSFETs. An 8 nm Al<sub>2</sub>O<sub>3</sub> film was regrown by ALD after removing the encapsulation layer by buffered oxide etch (BOE) solution and soaked in ammonia sulfide for 10 min for surface preparation. After 600 °C postdeposition anneal (PDA) in N<sub>2</sub> ambient, the source and drain Ohmic contacts were made by an electron beam evaporation of a combination of AuGe/Ni/Au for NMOSFETs or Pt/Ti/Pt/Au for PMOSFETs and a lift-off process, followed by a RTA process at 400 °C for 30 s also in a N<sub>2</sub> ambient. The gate electrode was defined by electron beam evaporation of Ni/Au and a lift-off process. It was found during the process that GaAs (111)A surface is more hydrophilic as In-rich InGaAs surface; GaAs (100) surface is more hydrophobic. Hydrophilic surface is believed to be favorable for ALD two-dimensional growth and good interface properties. 18

The fabricated MOSFETs have a nominal channel length varying from 0.75 to 40  $\mu$ m and a gate width of 100  $\mu$ m. A Keithley 4200 was used for MOSFET output characteristics. The full conductance measurement was carried out using an HP4284A precision LCR meter with frequencies varying from 100 Hz to 1 MHz. For the above process, the contact resistance on (111)A surface is 0.28  $\Omega$  mm for NMOSFET and 3.3  $\Omega$  mm for PMOSFET, and the sheet resistance is 180  $\Omega$ /sq for Si implanted *n*-type area and 4900  $\Omega$ /sq for Zn implanted p-type area. The contact resistance on (100) surface is 0.43  $\,\Omega$  mm for NMOSFET and 46.8  $\,\Omega$  mm for PMOSFET, and the sheet resistance is 550  $\Omega$ /sq for Si implanted *n*-type area and 30150  $\Omega$ /sq for Zn implanted p-type area. All these values are determined by the transmission line model method. Due to relatively larger lattice spacing on (111)A crystal plane, the contact resistance and sheet resistance obtained on (111)A are better than those on (100) under the same implantation and activation conditions.

0003-6951/2009/94(21)/212104/3/\$25.00

a) Author to whom correspondence should be addressed. Electronic mail: yep@purdue.edu.

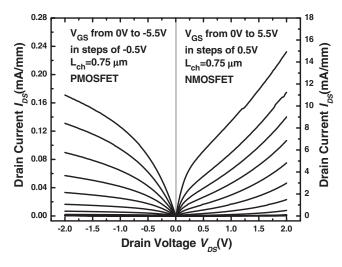

FIG. 1. I-V characteristics of a NMOSFET and a PMOSFET with 8 nm  $Al_2O_3$  as gate dielectric.

The drain current in an inversion-mode MOSFET is the detrimental tester for Fermi-level pinning or unpinning. Figure 1 shows the well-behaved I-V characteristics of both NMOSFET and PMOSFET on GaAs (111)A with channel length of 0.75  $\mu$ m. The maximum inversion drain current is 15 mA/mm for NMOSFET, which is among the highest values in inversion-mode GaAs MOSFETs with directly deposited oxides. 12-14 We ascribe the short-channel-effect like low output conductance on the 0.75  $\mu m$  NMOSFET to lateral interdiffusion of Si dopant implanted at source/drain regions and activated at 820 °C. It is significantly improved at channel length  $\geq 2 \mu m$  (not shown). The simple MEDICI simulation shows that only 0.2 pA/mm drain current is expected even without accounting interface traps if the Fermi-level is pinned at the midgap of GaAs with 0.75  $\mu$ m channel length and  $V_{\rm ds}$ =2 V. From the simulation, Fermi-level in the channel region must be less than 0.05 eV near the conduction band minimum (CBM) for drain current of 15 mA/mm due to nearly two orders of magnitude lower effective density of states at CBM in GaAs than Si. The drain current for PMOS-FET is 0.17 mA/mm, which is about two orders of magnitude lower than that for NMOSFET. However, it is not so surprising if we consider the hole mobility in bulk GaAs is 20 times smaller than the electron mobility. The contact resistance on fabricated PMOSFET is 3.3  $\Omega$  mm, which is also one order of magnitude higher than 0.28  $\Omega$  mm on NMOSFET.

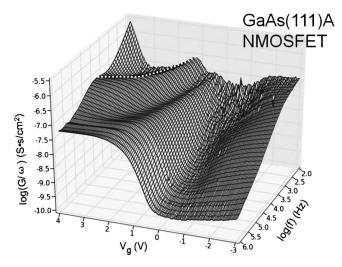

The conductance method is widely used to quantitatively evaluate interface trap states within the semiconductor bandgap. At any given frequency of ac gate voltage, the energy loss from charge trapping and detrapping at Al<sub>2</sub>O<sub>3</sub>/GaAs interface states depends both on the speed of response of interface traps and on the interface trap density near the Fermi level at GaAs surface. The energy loss, measured as an equivalent parallel conductance G, has its maximum when the energy level of the trap states is aligned with the GaAs surface Fermi level. The full  $G/\omega - V_{\rm g} - f$  measurement is developed by utilizing the location of the normalized conductance peaks to illustrate the Fermi-level movement at the Al<sub>2</sub>O<sub>3</sub>/GaAs interface, because the measured frequency is transformable to the detected trap energy level and Fermi level in the bandgap. 19 Figure 2 shows an ensemble of  $G/\omega - V_{\rm g}$  measurements at 30 different frequencies between

FIG. 2.  $G/\omega - V_g - f$  plot measured on the same NMOSFET clearly showing the Fermi-level movement at inversion region with the gate bias. The dashed white line is guide to the eyes.

100 Hz and 1 MHz on the same 0.75  $\mu$ m GaAs (111)A NMOSFET. The dashed white line illustrates the Fermi-level movement versus gate bias within GaAs bandgap at the Al<sub>2</sub>O<sub>3</sub>/GaAs interface. The conductance peaks are from the inverted minority carriers (electrons for NMOSFETs). No conductance peaks from majority carriers are observed since it is fabricated on semi-insulating substrates. Tracing by the conductance peak, Fermi-level is clearly moved by changing the gate bias. The interface trap density  $D_{\rm it}$  of ~2  $\times$  10<sup>12</sup> cm<sup>2</sup> eV is determined at upper half bandgap of GaAs (111)A from the measured magnitude of conductance peaks. Similar Fermi-level movement from tracing the conductance peaks is also observed on PMOSFETs where the energy loss is from trapping and detrapping of minority carrier holes (not shown).

Surprisingly, NMOSFETs processed at the same time on GaAs (100) substrates with the same gate length and oxide thickness have the maximum drain current of only  $\sim 1~\mu A/\text{mm}$ . Meanwhile, PMOSFETs on GaAs (100) have the maximum drain current of 0.8 mA/mm, a factor of five larger than that on GaAs (111)A. All these seemingly randomly distributed experimental results are well explained by the following proposed empirical model as shown in Fig. 3. It is based on the unified disorder induced gap state (DIGS) model proposed by Hasegawa and Ohno in 1986, which explains the striking correlation between the energy location

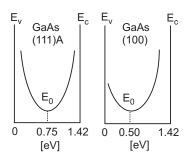

FIG. 3. Empirical model after Refs. 20–22. 0.75 eV is associated with a missing anion due to Ga (111)A surface; 0.5 eV is associated with a missing cation, which is the case most likely for (100) or (110) (Ref. 22). The minimum  $D_{\rm it}$  and U-shape curvature depends on processing conditions, while the location of  $E_0$  remains constant for each semiconductor with the same crystal facet.

$E_{\rm min}$  for the minimum interface state density at the insulatorsemiconductor interface and the Fermi-level pinning position  $E_{\rm pin}$  of the metal-semiconductor interface. The central concept is that there is an energy level called trap neutral level  $E_0$  at the high-k/GaAs interface, <sup>21</sup> above which the trap states are of acceptor type or electron traps and below which are of donor type or hole traps.  $E_0$  is at the same or similar energy level as  $E_{\min}$ ,  $E_{\text{pin}}$ , and  $E_{\text{HO}}$  in Ref. 20. By photoemission and other experiments, Spicer *et al.*<sup>22</sup> discovered that  $E_{pin}$  in GaAs is 0.75 and 0.5 eV above the valence band maximum (VBM). The first energy given is associated with a missing anion (As) and the second with a missing cation (Ga). Ignoring the complications of surface reconstructions, GaAs (111)A surface is a Ga-terminated polar surface, which can be regarded as a missing anion (As) surface with  $E_0$ =0.75 eV above VBM. <sup>22,23</sup> GaAs (100) is a Ga-As terminated nonpolar surface which might be more related with missing cations with  $E_0$ =0.5 eV above VBM, as shown in Fig. 3. The drain current strongly depends on the energy separation between  $E_0$  and CBM for NMOSFET or VBM for PMOSFET. With the measured near midgap interface trap density  $D_{\rm it}$  of  $2 \times 10^{12}$  cm<sup>2</sup> eV, the less the separation is, the less traps are filled in to prevent further Fermi-level movement for strong inversion, the more inversion charge and drain current can be achieved. <sup>21</sup> This model explains why NMOSFET on GaAs (111)A outperforms that on (100), and PMOSFET on GaAs (100) outperforms that on (111)A. It also explains why the frequency dispersion in accumulation is much better for PMOS capacitors than for NMOS capacitors on (100) and why it is similar on (111)A (not shown).

In conclusion, GaAs inversion-mode MOSFETs with ALD Al<sub>2</sub>O<sub>3</sub> as gate dielectrics are fabricated on (111)A and (100) surfaces. Maximum drain current of 15 mA/mm is obtained on GaAs (111)A NMOSFET with the channel length of 0.75  $\mu$ m. The original surface condition and the chemical based surface preparation before the dielectric deposition is the key to realize the unpinning of the Fermi level on GaAs. For example, Fermi level on GaAs (100) with SiH<sub>4</sub> passivation has recently been demonstrated unpinned. 16,17 Even the large discrepancy of 1  $\mu$ A/mm drain current reported in this Letter and 4.5 mA/mm reported in Ref. 14 on GaAs (100) NMOSFETs using the same directly ALD Al<sub>2</sub>O<sub>3</sub> as gate dielectrics could be related with some detailed difference on surface chemistry and process. Fermi-level pinning at the midgap of GaAs as proposed by the unified defect model<sup>22</sup> can be overcome by the appropriate surface preparation and the right dielectric deposition technique. More systematic studies on GaAs (111)B, (110), and (100) surfaces are ongoing for more conclusive experimental evidences. After submission of this manuscript, we became aware of the theoretical work with more accurate description of the related model.24

The authors would like to thank J. Robertson, R. M. Wallace, H. Hasegawa, T. Yasuda, K. Xu, B. Yang, and K. K. Ng for the valuable discussions and K. Martens and H. C. Lin for the technical assistance. The work is supported by National Science Foundation under Grant ECS-0621949, the SRC FCRP MSD Focus Center, and DoD ARO DURIP program.

<sup>1</sup>Y. Xuan, Y. Q. Wu, and P. D. Ye, IEEE Electron Device Lett. **29**, 294 (2008).

<sup>2</sup>N. Goel, D. Heh, S. Koveshnikov, I. Ok, S. Oktyabrsky, V. Tokranov, R. Kambhampati, M. Yakimov, Y. Sun, P. Pianetta, C. K. Gaspe, M. B. Santos, J. Lee, S. Datta, P. Majhi, and W. Tsai, Tech. Dig. - Int. Electron Devices Meet. 2008, 363.

<sup>3</sup>Y. Sun, E.W. Kiewra, J.P. de Souza, J.J. Bucchignano, K.E. Fogel, D.K. Sadana, and G.G. Shahidi, Tech. Dig. - Int. Electron Devices Meet. **2008**, 367

<sup>4</sup>J. Lin, S. Lee, H.J. Oh, W. Yang, G.Q. Lo, D.L. Kwong, and D.Z. Chi, Tech. Dig. - Int. Electron Devices Meet. **2008**, 401.

<sup>5</sup>T. D. Lin, H. C. Chiu, P. Chang, L. T. Tung, C. P. Chen, M. Hong, J. Kwo, and W. Tsai, Appl. Phys. Lett. **93**, 033516 (2008).

<sup>6</sup>D. Shahrjerdi, T. Rotter, G. Balakrishnan, D. Huffaker, E. Tutuc, and S. K. Banerjee, IEEE Electron Device Lett. **29**, 557 (2008).

<sup>7</sup>H. Zhao, F. Zhu, Y. T. Chen, J. H. Yum, Y. Wang, and J. C. Lee, Appl. Phys. Lett. **94**, 093505 (2009).

<sup>8</sup>A. M. Sonnet, C. L. Hinkle, M. N. Jivani, R. A. Chapman, G. P. Pollack, R. M. Wallace, and E. M. Vogel, Appl. Phys. Lett. **93**, 122109 (2008).

<sup>9</sup>Y. Xuan, Y.Q. Wu, T. Shen, T. Yang, and P.D. Ye, Tech. Dig. - Int. Electron Devices Meet. **2007**, 637.

<sup>10</sup>H. C. Lin, W. Wang, G. Brammertz, M. Meuris, and M. Heyns, Proceedings of the 40th IEEE Semiconductor Interface Specialist Conference, 2008 (unpublished).

<sup>11</sup>M. Xu, Y. Xuan, Y. Q. Wu, T. Shen, and P. D. Ye, Proceedings of the 40th IEEE Semiconductor Interface Specialist Conference, 2008 (unpublished).

<sup>12</sup>Y. Xuan, H. C. Lin, P. D. Ye, and G. D. Wilk, Appl. Phys. Lett. 88, 263518 (2006).

<sup>13</sup>F. Ren, M. Hong, W. S. Hobson, J. M. Kuo, J. R. Lothian, J. P. Mannaerts, J. Kwo, S. N. G. Chu, Y. K. Chen, and A. Y. Cho, Solid-State Electron. 41, 1751 (1997).

<sup>14</sup>D. Shahrjerdi, T. Akyol, M. Ramon, D. I. Garcia-Gutierrez, E. Tutuc, and S. K. Banerjee, Appl. Phys. Lett. **92**, 203505 (2008).

<sup>15</sup>I. Ok, H. Kim, M. Zhang, T. Lee, F. Zhu, L. Yu, S. Koveshnikov, W. Tsai, V. Tokranov, M. Yakimov, S. Oktyabrsky, and J.C. Lee, Tech. Dig. - Int. Electron Devices Meet. **2006**, 346742.

<sup>16</sup>J. P. de Souza, E. Kiewra, Y. Sun, A. Callegari, D. K. Sadana, G. Shahidi, D. J. Webb, J. Fompeyrine, R. Germann, C. Rossel, and C. Marchiori, Appl. Phys. Lett. **92**, 153508 (2008).

<sup>17</sup>H. C. Chin, M. Zhu, S. J. Whang, C. H. Tung, G. S. Samudra, and Y. C. Yeo, IEEE Electron Device Lett. 29, 553 (2008).

<sup>18</sup>Y. Xuan, H. C. Lin, and P. D. Ye, IEEE Trans. Electron Devices 54, 1811 (2007).

<sup>19</sup>G. Brammertz, K. Martens, S. Sioncke, A. Delabie, M. Caymax, M. Meuris, and M. Heyns, Appl. Phys. Lett. 91, 133510 (2007).

<sup>20</sup>H. Hasegawa and H. Ohno, J. Vac. Sci. Technol. B **4**, 1130 (1986).

<sup>21</sup>P. D. Ye, J. Vac. Sci. Technol. A **26**, 697 (2008).

<sup>22</sup>W. E. Spicer, P. W. Chye, P. R. Skeath, C. Y. Su, and I. Lindau, J. Vac. Sci. Technol. 16, 1422 (1979).

<sup>23</sup>T. Yasuda, N. Miyata, H. Ishii, T. Itatani, O. Ichikawa, N. Fukuhara, M. Hata, A. Ohtake, T. Haimoto, T. Hoshii, M. Takenaka, and S. Takagi, Proceeding of the 40th IEEE Semiconductor Interface Specialist Conference, 2008 (unpublished).

<sup>24</sup>J. Robertson, Appl. Phys. Lett. **94**, 152104 (2009).